Write DMA RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 449

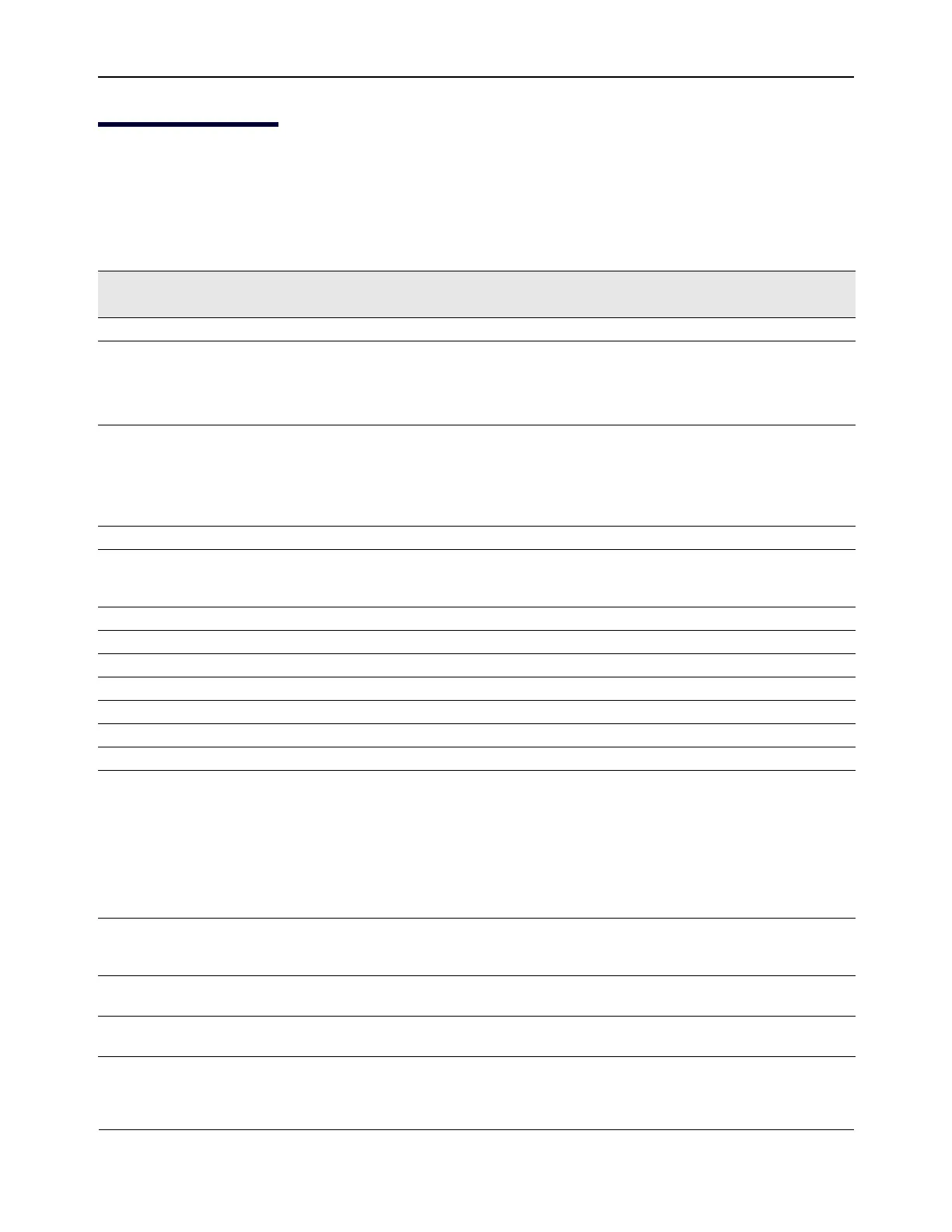

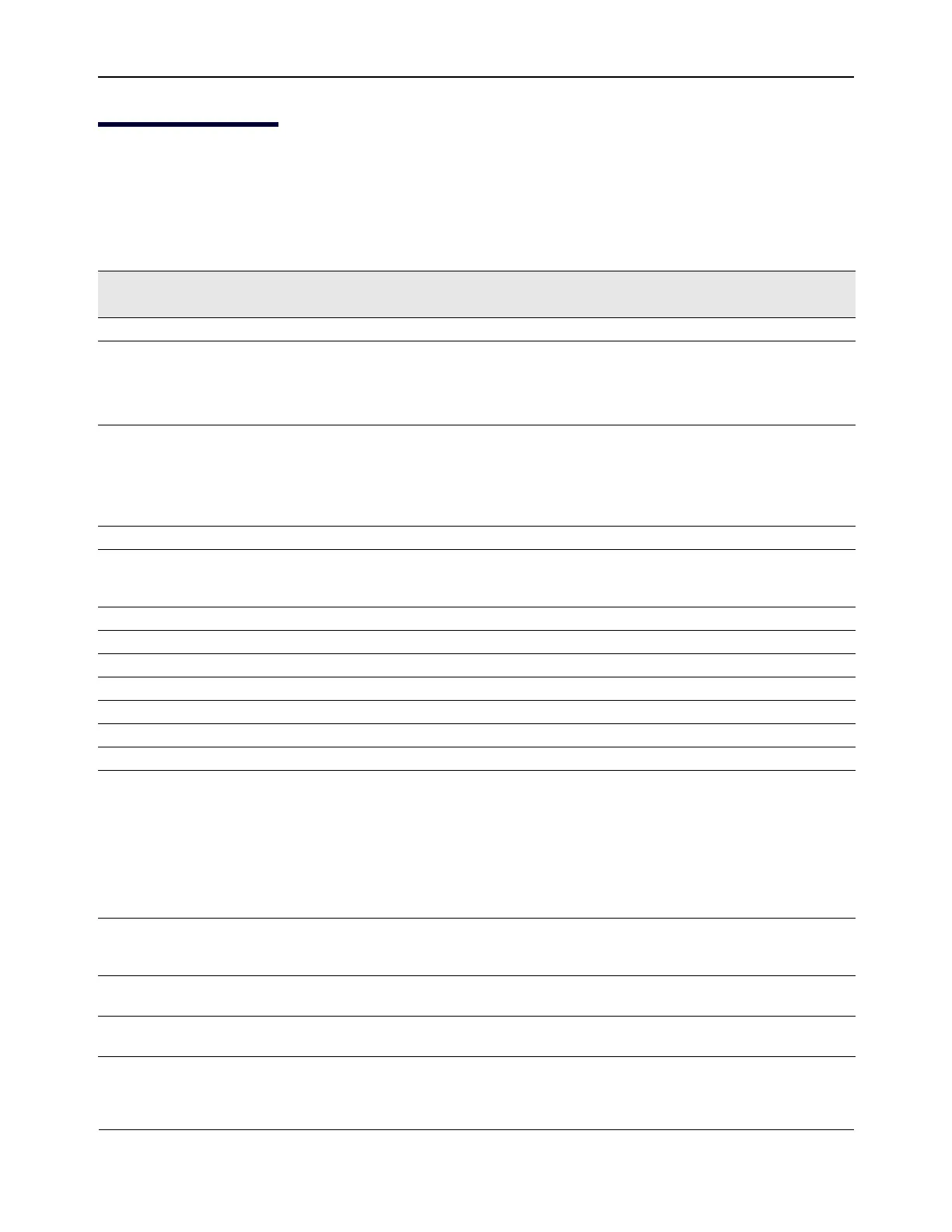

Write DMA Registers

All registers reset are core reset unless specified.

Write DMA Mode Register (offset: 0x4C00)

Name Bits Access

Default

Value

Description

Reserved 31:30 RO 0 –

Enable FIX for host coalescing

bug

29 RW 0 1: Enable the FIX

0: Disable the FIX

To Fix the bug that device will send out Status

Block before the interrupt message.

(BCM5719/5720 only) WDMA

small packet improvement

disable

28 RW 0 wdma_small_packet_improvement_disable

0: Use new local RRR data instead of fetching

from RBD memory (default enable).

1: Use old implementation to fetch RRR data

from RBD memory.

Reserved 28:19 RO 0 –

Swap Test Enable 18 RW 0 When this bit is set, swap test mode will be

enabled and bits 17 to 12 can be used to test

different byte/word swap settings.

HC Byte Swap 17 RW 0 Byte swap control for status words.

HC Word Swap 16 RW 0 Word swap control for status words.

BD Byte Swap 15 RW 0 Byte swap control for return BDs.

BD Word Swap 14 RW 0 Word swap control for return BDs

Data Byte Swap 13 RW 0 Byte swap control for data.

Data Word Swap 12 RW 0 Word swap control for data.

Software Byte Swap Control 11 RW 0 To override byte enables with all 1's.

Receive Accelerate mode 10 RW 0 The write DMA-to-PCI request length is the

available data size in the PCI RX FIFO.

Set to 1: The write DMA-to-PCI request length is

the maximum length of the current transaction,

regardless of the available data size in PCI RX

FIFO. This mode cannot be used in slow core

clock environment. Disable this mode before

switching to slow core clock mode.

Write DMA Local Memory 9 RW 0 Attention Enable. Enable Write DMA Local

Memory Read Longer Than DMA Length

Attention.

Write DMA PCI FIFO Overwrite

Attention Enable

8 RW 0 Enable Write DMA PCI FIFO Overwrite Attention

(PCI write longer than DMA length).

Write DMA PCI FIFO Underrun

Attention Enable

7 RW 0 Enable Write DMA PCI FIFO Underrun Attention.

Loading...

Loading...