SerDes PHY Register DefinitionsBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 564

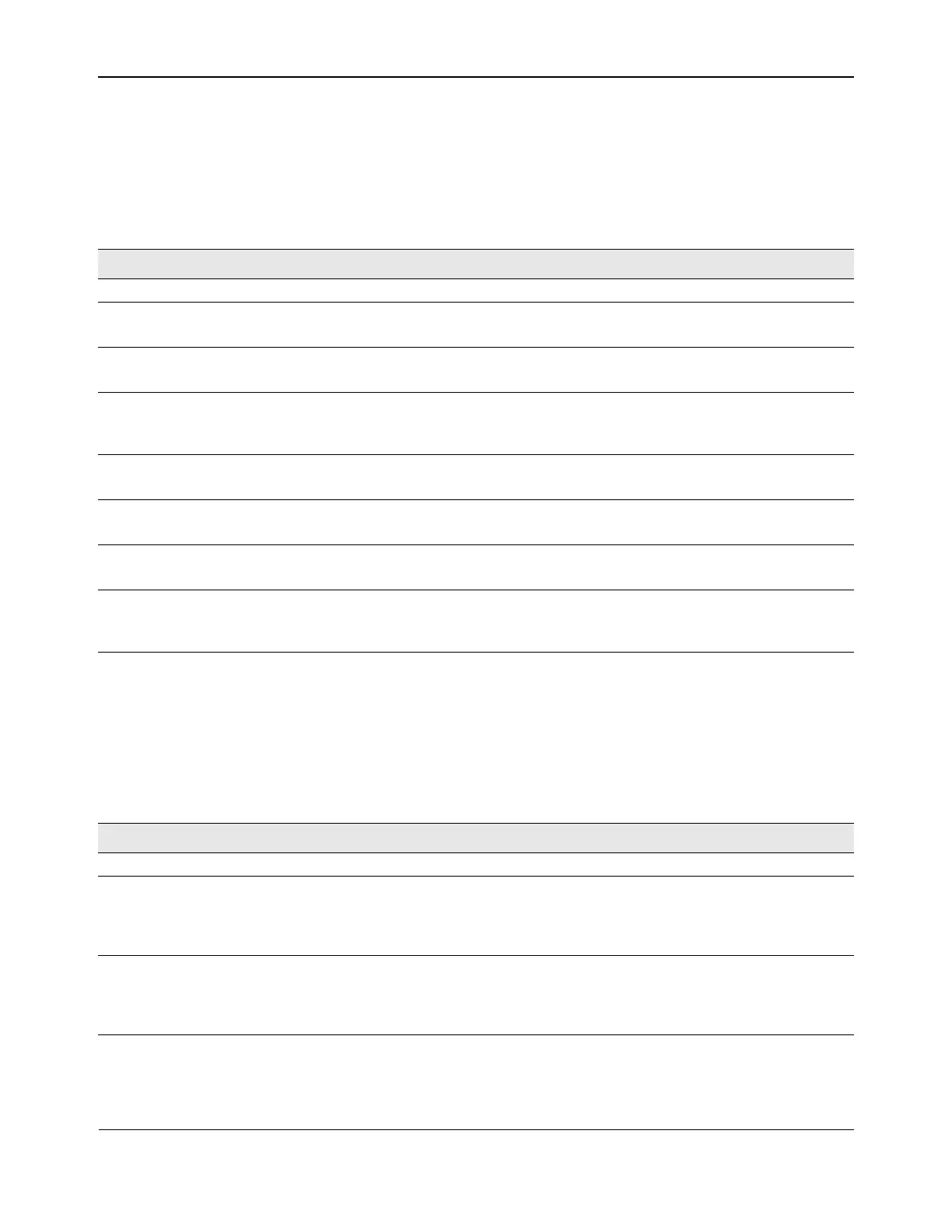

FXCONTROL3

Register Description: 100FX control register

Register Offset: 0x12 at Block 2

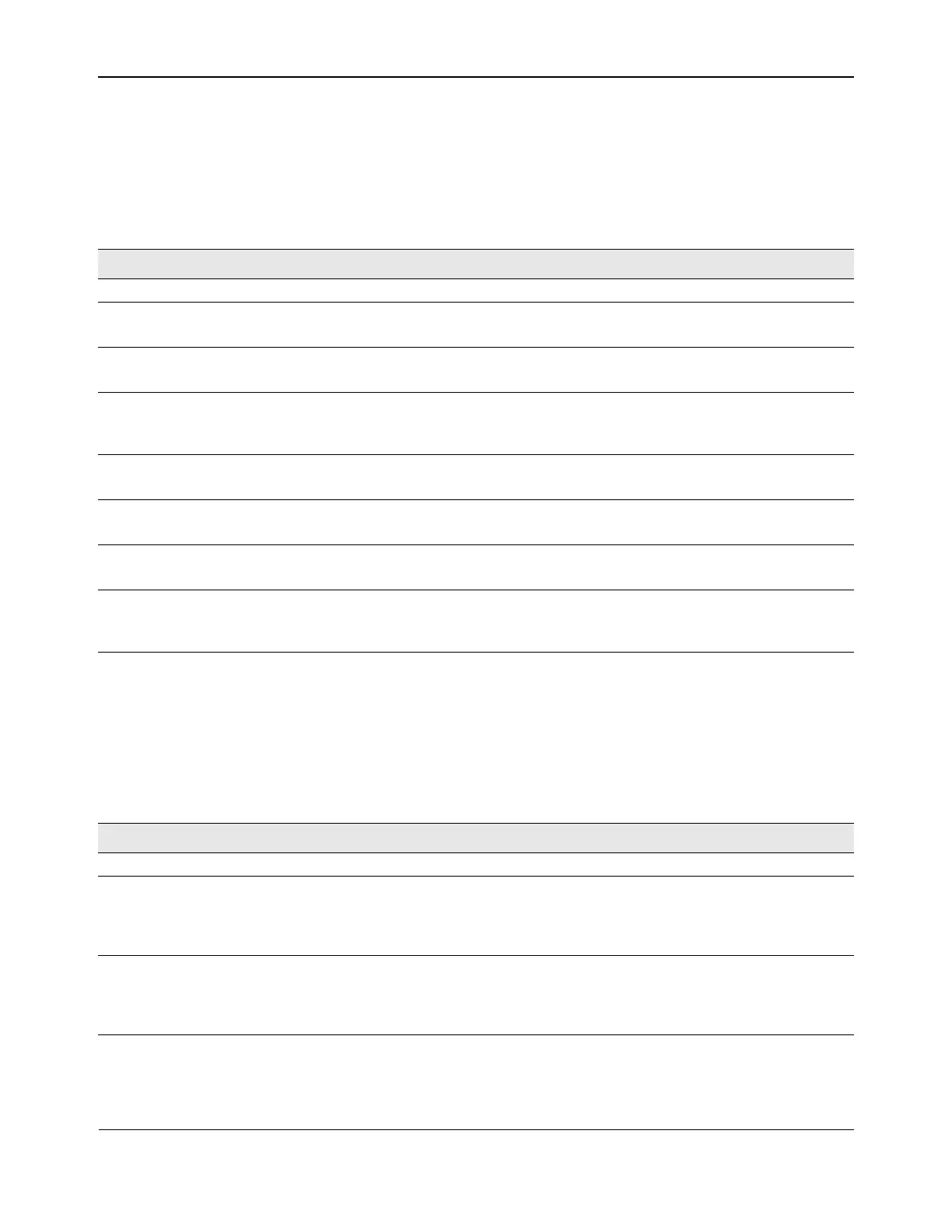

FXSTATUS1

Register Description: 100FX link status register

Register Offset: 0x13 at Block 2

Table 142: FXCONTROL3

Bits Name RW Description Default

15:7 RESERVED RW Reserved 0x000

6 FX100_BYPASS_NRZ RW 1 = Bypass NRZ encoder in 100FX mode

0 = Normal operation

0

5 FX100_BYPASS_ENCODER RW 1 = Bypass 4B5B encoder in 100FX mode

0 = Normal operation

0

4 FX100_BYPASS_ALIGNMEN

T

RW 1 = Bypass 5B code group alignment in 100FX

mode

0 = Normal operation

0

3 FX100_FORCE_LINK RW 1 = Force link in 100FX mode

0 = Normal operation

0

2 FX100_FORCE_LOCK RW 1 = Force lock in 100FX mode

0 = Normal operation

0

1 FX100_FAST_UNLOCK_TIM

ER

RW 1 = Speed up unlock timer in 100FX mode

0 = Normal operation

0

0 FX100_FAST_TIMER RW 1 = Speed up timer to acquire lock and link (test

vectors and simulation) in 100FX mode

0 = Normal operation

0

Table 143: FXSTATUS1

Bits Name RW Description Default

15:10 RESERVED RW Reserved 0x00

9 FX100_LINK_STATUS_CHG RO/LH 1 = 100-FX mode link status change since

last read

0 = 100-FX mode link status has not changed

since last read

0

8 FX100_BAD_ESD_DETECTED RO/LH 1 = 100-FX mode bad ESD error detected

since last read (premature end)

0 = No 100-FX mode bad ESD error detected

since last read

0

Loading...

Loading...