PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 281

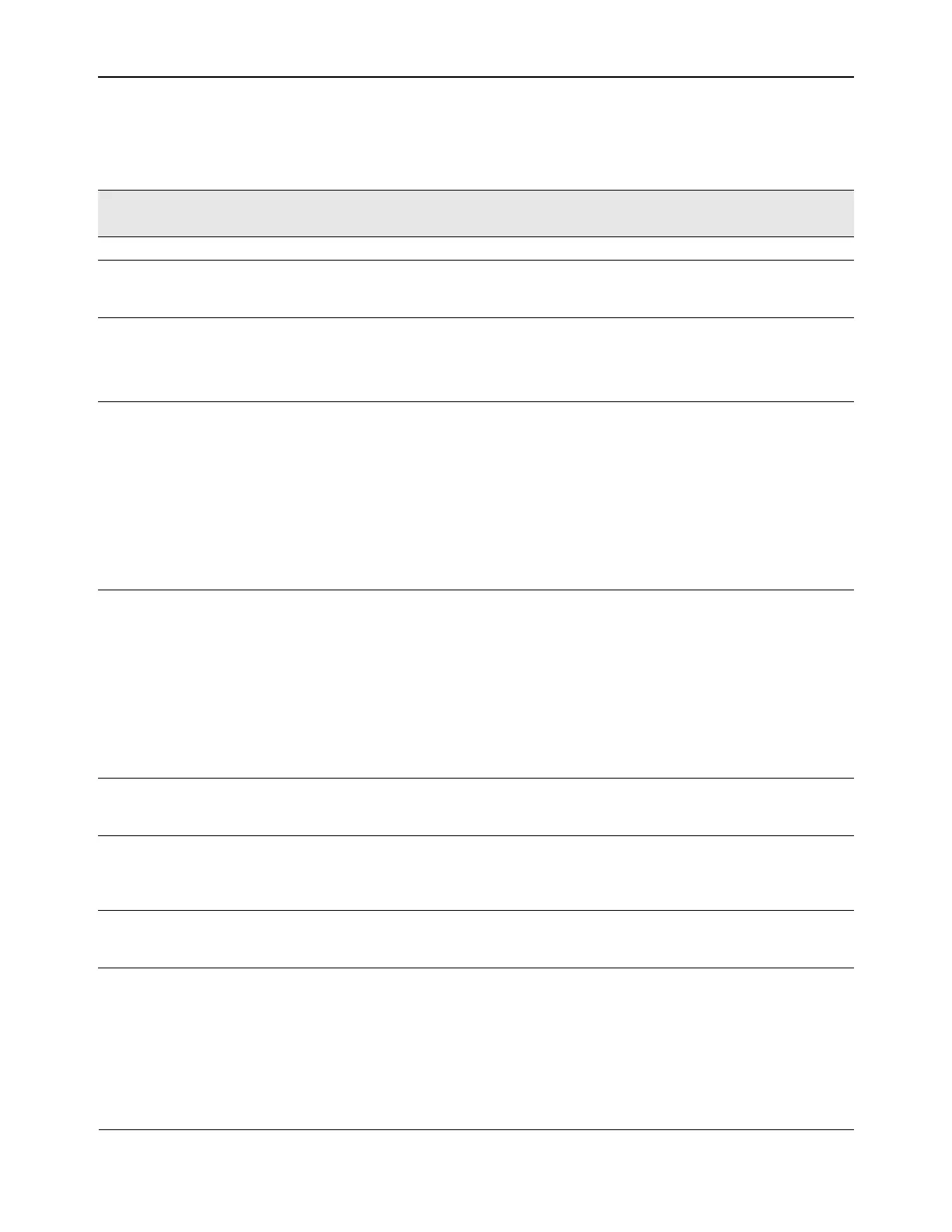

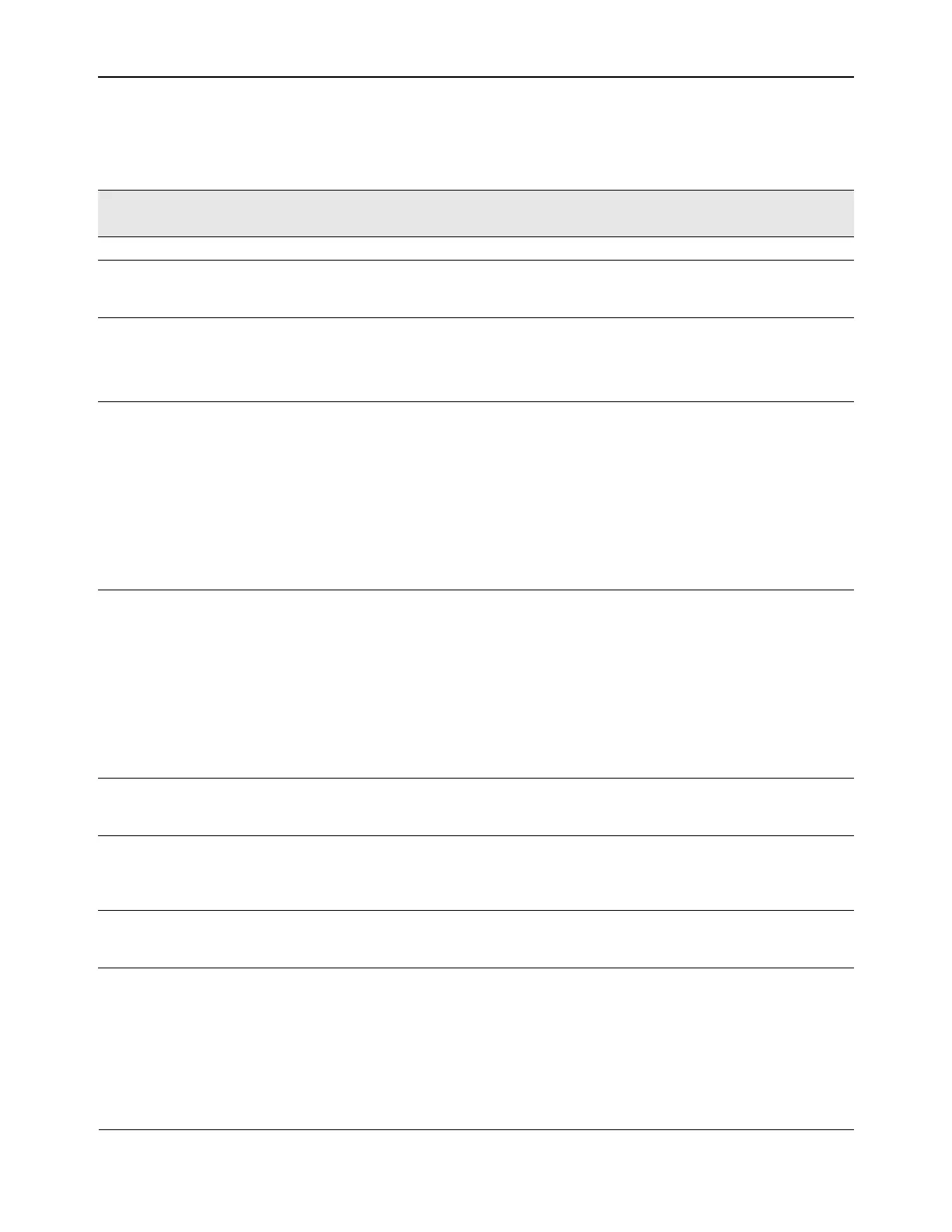

MSI Capability Header (offset: 0x58)

The device driver is prohibited from writing to this register.

Name Bits Access

Default

Value

Description

MSI Control 31:25 RO 0x00 Reserved

MSI_PVMASK_

CAPABLE

24 RO 0 This bit indicates if the function supports per vector

masking. This value comes from the MSI_PV_MASK_CAP

bit in the register space.

64-bit Address

Capable

23 RO 1 Hardwired

Advertise 64-bit address capable

This bit indicates that the chip is capable of generating 64

bit MSI messages.

Multiple Message

Enable

22:20 RW 0x0 These bits indicate the number of message that the chip is

configured (allowed) to generate. Number of allocated

message:

0 1 Chip is set to generate 1 message

1 2 Chip is set to generate 2 messages

2 4 Chip is set to generate 4 messages

3 8 Chip is set to generate 8 messages

4 16 Chip is set to generate 16 messages

5 32 Chip is set to generate 32 messages

Multiple Message

Capable

19:17 RO 0x3 These bits indicate the number of messages that the chip

is capable of generating. This value comes from the bit in

the register space. Number of requested message:

0 1 Chip is set to generate 1 message

1 2 Chip is set to generate 2 messages

2 4 Chip is set to generate 4 messages

3 8 Chip is set to generate 8 messages

4 16 Chip is set to generate 16 messages

5 32 Chip is set to generate 32 messages

MSI Enable 16 RW 0 When this bit is set, the chip will generate MSI cycles to

indicate interrupts instead of asserting the INTA# pin.

When this bit is zero, the INTA# pin will be used.

Next Capability

Pointer

15:8 RO A0 This value continues the PCI capability chain. It's value

specified an offset in the PCI address space of the next

capability. The read-only value of this register is controlled

by the CAP_ENA register in the PCI register space.

MSI capability ID 7:0 RO 0x5 The 8-bit MSI Capability ID is set to 5 to indicate that the

next 8 bytes are a Message Signaled Interrupt capability

block.

Loading...

Loading...