Miscellaneous Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 480

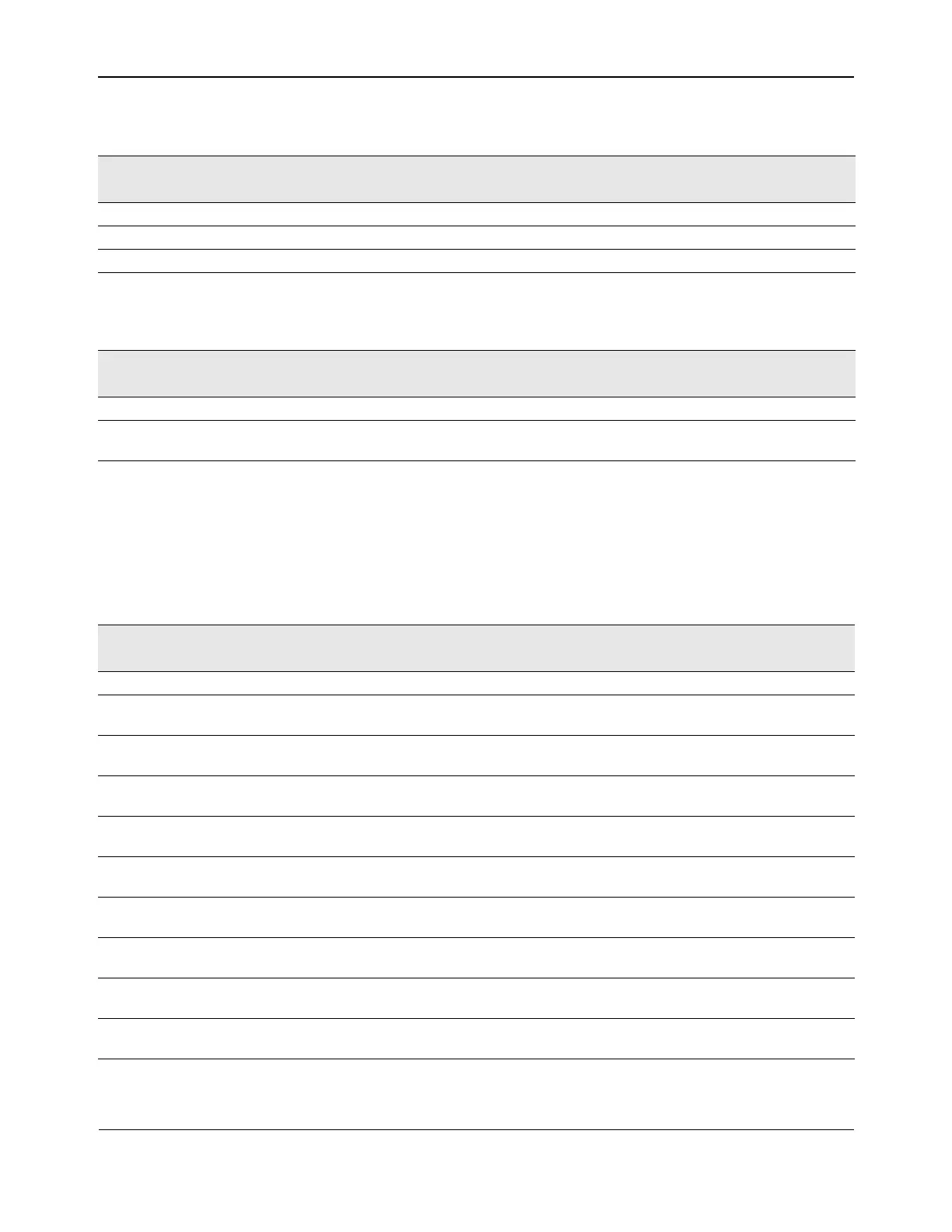

Mem TM control 3(offset: 0x68E8)

Expansion ROM Address Register (offset: 0x68EC)

BCM5719/BCM5720 Registers

The registers in this section are available only for the BCM5719 and BCM5720.

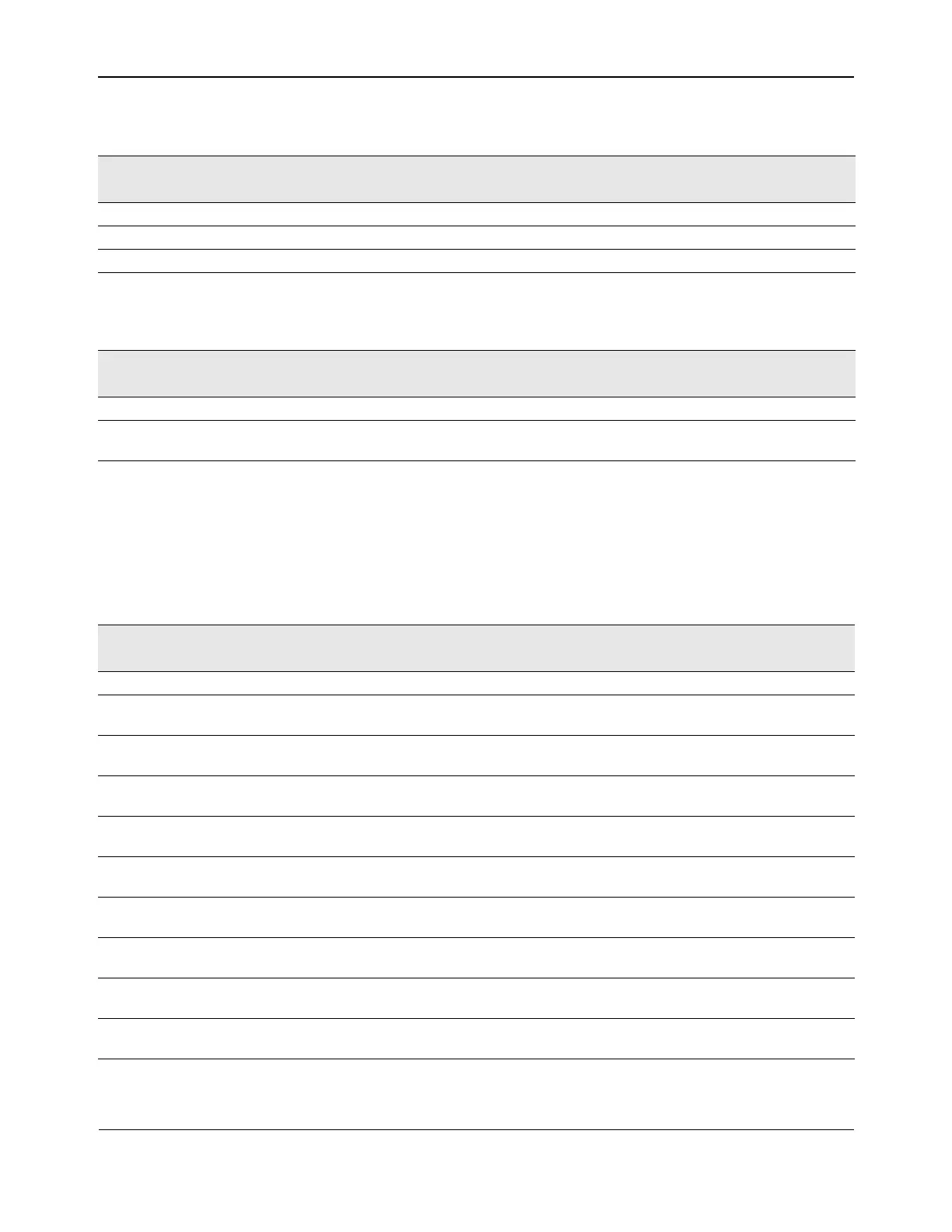

Mem TM Control 4 (offset: 0x68F8)

Name Bits Access

Default

Value

Description

Reserved 31:9 RW 0x0 –

Memory TM control boot rom 8:4 RW 0x00 TM control for rom

Memory TM control scratchpad 3:0 RW 0x00 TM control for scratchpad

Name Bits Access

Default

Value

Description

Expansion ROM Test bits 31:24 RW 0 Reserved–keep at 0 for normal operation.

Expansion ROM base address 23:0 RW 0 Expansion ROM base address, expect to be d-

word aligned.

Name Bits Access

Default

Value

Description

Reserved 31:28 RW 0x0 Reserved

WDMA FIFO tmb

control

27:26 RW 0x00 TM control for WDMA engine memory.

WDMA FIFO tma

control

25:24 RW 0x00 TM control for WDMA engine memory.

Non-LSO Ch3 RDMA

FIFO tmb control

23:22 RW 0x00 TM control for Ch3 non-LSO RDMA engine memory.

Non-LSO Ch3 RDMA

FIFO tma control

21:20 RW 0x00 TM control for Ch3 non-LSO RDMA engine memory.

Non-LSO Ch2 RDMA

FIFO tmb control

19:18 RW 0x00 TM control for Ch2 non-LSO RDMA engine memory.

Non-LSO Ch2 RDMA

FIFO tma control

17:16 RW 0x00 TM control for Ch2 non-LSO RDMA engine memory.

Non-LSO Ch1 RDMA

FIFO tmb control

15:14 RW 0x00 TM control for Ch1 non-LSO RDMA engine memory.

Non-LSO Ch1 RDMA

FIFO tma control

13:12 RW 0x00 TM control for Ch1 non-LSO RDMA engine memory.

Non-LSO Ch0 RDMA

FIFO tmb control

11:10 RW 0x00 TM control for Ch0 non-LSO RDMA engine memory.

Loading...

Loading...