RDMA RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 442

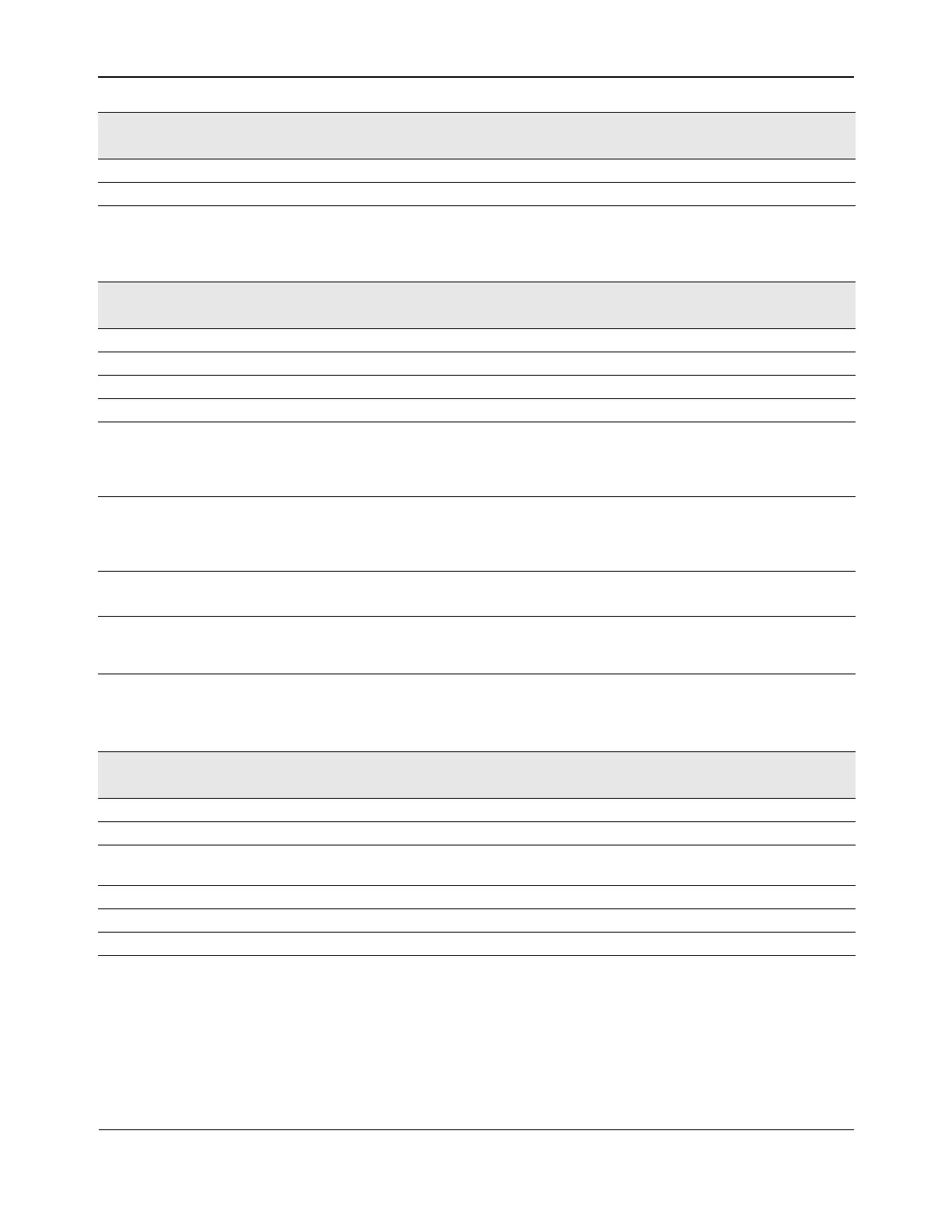

BD READ DMA Reserved Control Register (offset: 0x4A70)

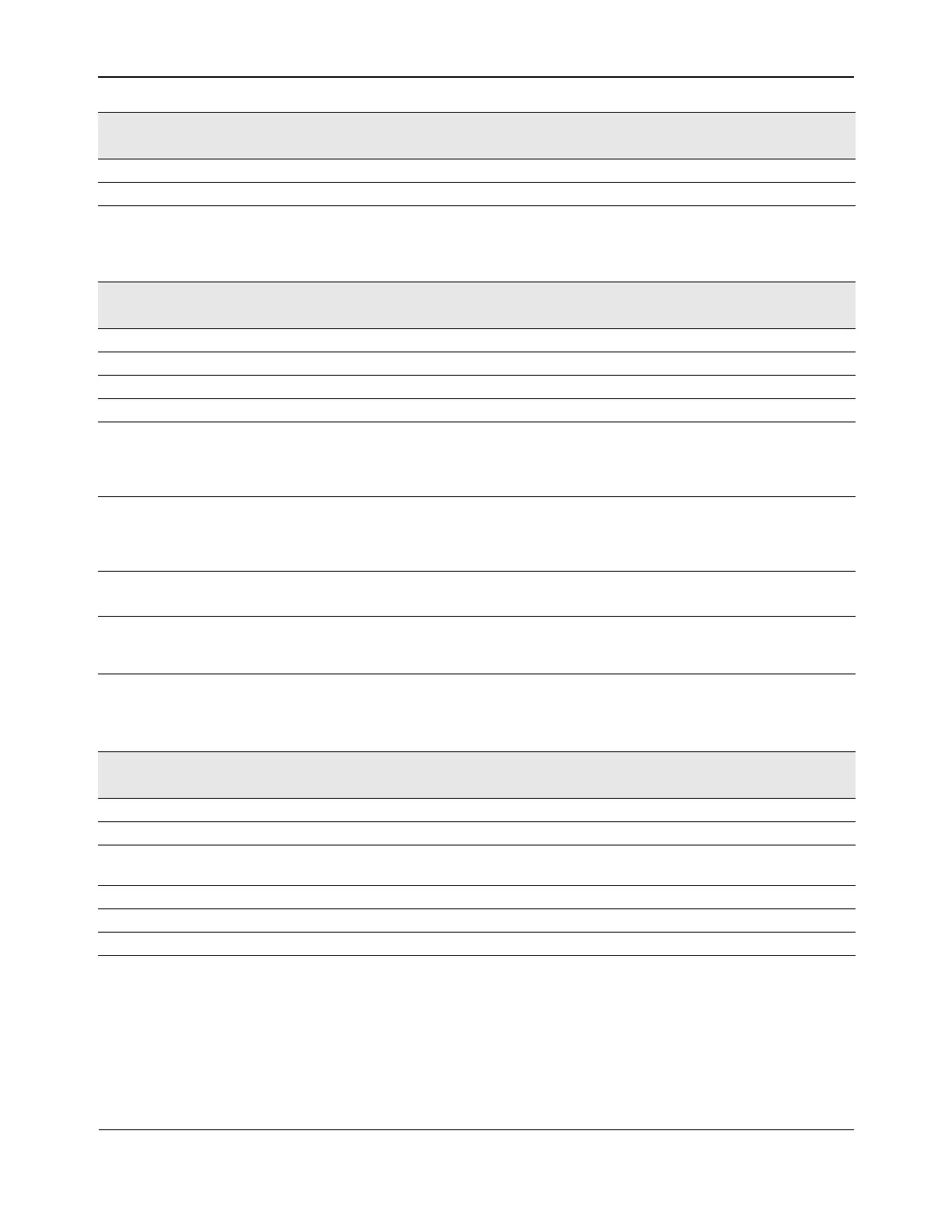

BD READ DMA Flow Reserved Control Register (offset: 0x4A74)

Read DMA PCI Target Abort 2 W2C 0 Read DMA PCI Target Abort Error.

Reserved 1:0 RO 0 –

Name Bits Access

Default

Value

Description

Txmbuf_margin 31:21 RO 0 –

Reserved 20 RO 0 –

FIFO High Mark 19:12 RO 0x90 –

FIFO Low Mark 11:4 RO 0x40 –

Slow Clock Fix Disable 3 RO 0 When cleared, it enables the fix to cover a corner

case in the link idle mode to allow the DMA Read

request to be generated when the core clock is

transitioning from slow to fast.

Stop communicating after

heavy stress Fix

2 RO 0 When set, this bit enables the fix for DMA FIFO

overrun occurs if a large number of Rx BDs are

fetched while the Tx MBUF is full and the Read

DMA FIFO is empty.

Late Collision Fix Enable 1 RO 0 0: Disable Fix

1: Enable Fix

Select FED Enable 0 RO 0 Ensure only 1 request is generated upon any

condition where the core clock is switching from

slow to fast or vice-versa.

Name Bits Access

Default

Value

Description

Fifo_threshold_bd_req 31:24 RO 0 –

Fifo_threshold_mbuf_req 23:16 RO 0x30 –

MBUF Threshold MBUF

Request

15:8 RO 0x54 –

Reserved 7 RO 0 –

Clock Request Fix Enable 6 RO 0 –

MBUF Threshold Clk Req 5:0 RO 0x7 –

Name Bits Access

Default

Value

Description

Loading...

Loading...