RDMA RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 448

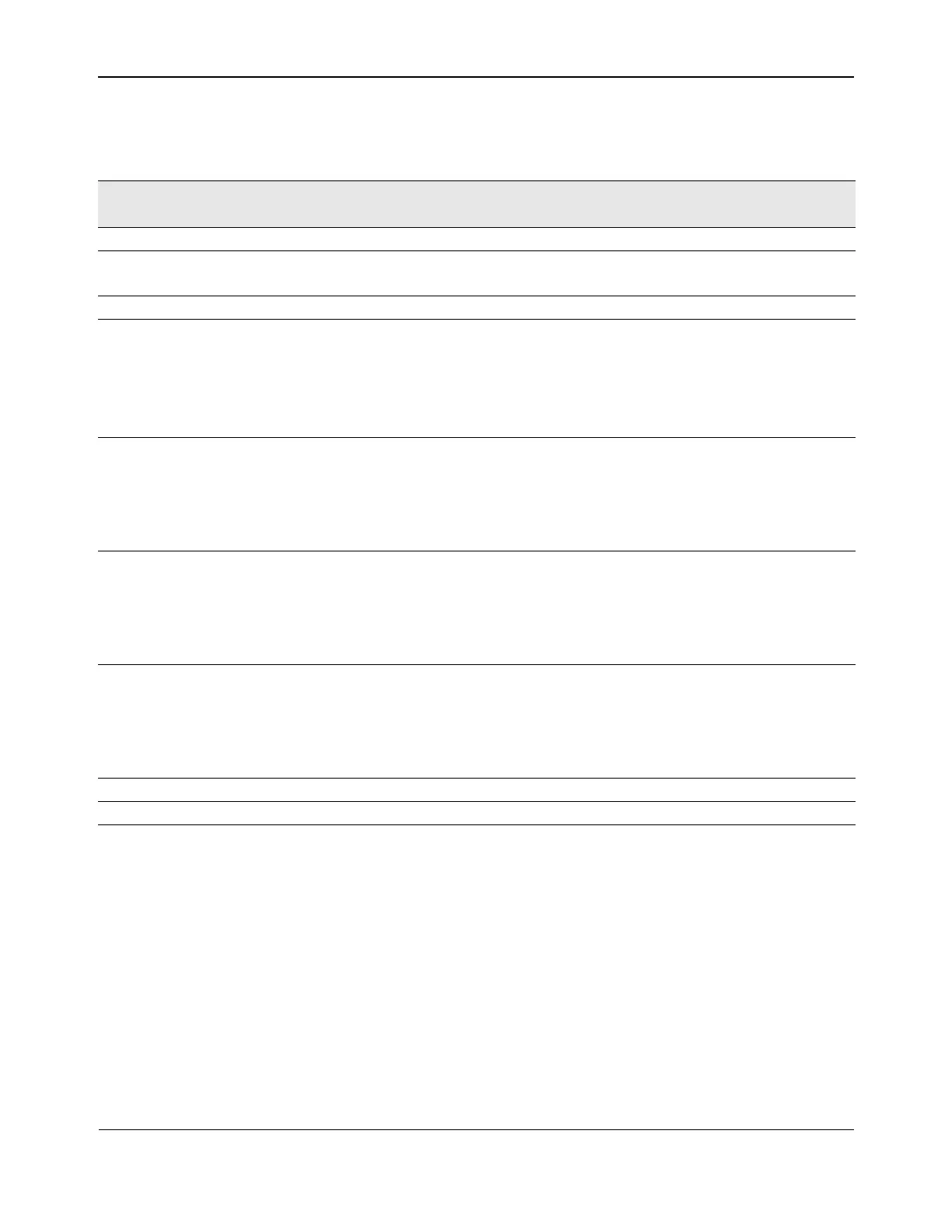

Non-LSO Read DMA Corruption Enable Control Register

(offset: 0x4B7C)

Name Bits Access

Default

Value

Description

Reserved 31:8 RO 0 –

Enable hardware fix for wrong

TCP checksum

7 RO 0 0: Enable Fix

1: Disable Fix

Reserved 6 RO 0 –

Enable hardware fix for IP

Header checksum corruption

5 RO 0 This control bit is used to enable the fix for the IP

Header Checksum Corruption occurs when an

IPV4 payload contents match an IPV6 Header

Type.

1: Disable fix

0: enable fix

DMA Read Engine may be

unable to generate Memory

Read Request to PCIE Core

upon transitioning from L1 to

L0 with Clkreq Enable

4 RO 1 Set to 1 to enable fix for clock request gap

problem of Tx Read DMA lock-up issue.

Note that increasing the ASPM L1 entry time to a

value on the order of 1ms is recommended and

may prevent this issue from occurring. See

register 0x7d28.

Enable hardware fix for clock

switching problem

3 RO 1 Set to 1 to enable fix for clock switching problem

of Tx Read DMA lock-up issue.

Note that increasing the ASPM L1 entry time to a

value on the order of 1ms is recommended and

may prevent this issue from occurring. See

register 0x7d28.

Enable hardware fix for PCIE

client lockup

2 RO 1 Set to 1 to enable fix for Tx Read DMA lock-up

issue.

Note that increasing the ASPM L1 entry time to a

value on the order of 1ms is recommended and

may prevent this issue from occurring. See

register 0x7d28.

Reserved 1 RO 0 –

Reserved 0 RO 0 –

Loading...

Loading...