Central Power Management Unit (CPMU) RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 387

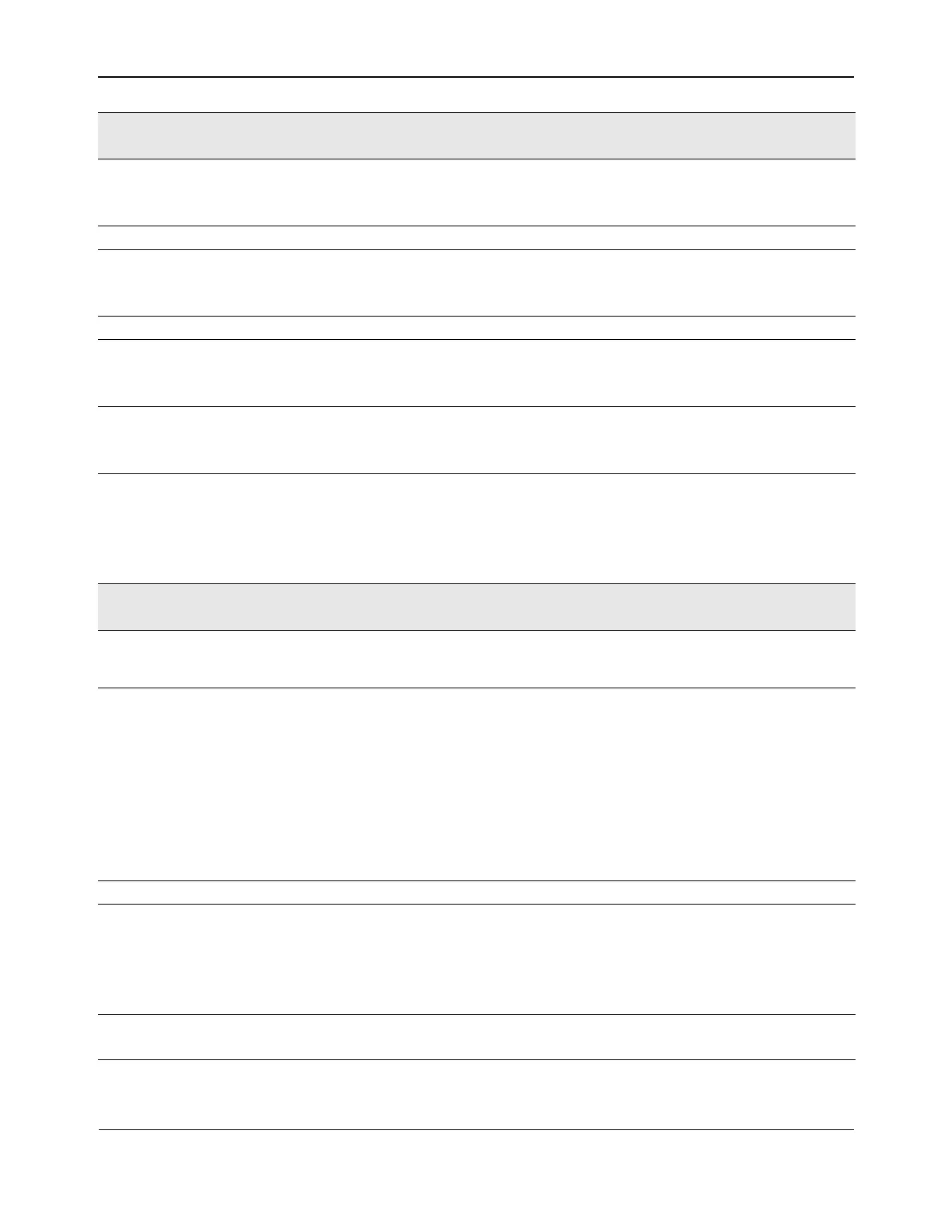

Status Register (offset: 0x362C)

This register is reset by POR Reset or CPMU Register Software Reset.

Flash Clock Speed Override

Enable

11 RW 0x0 Enable Flash clock override*.

1: Enable

0: Disable

Reserved 10:7 DC 0x0 –

Force Flash Clock Disable 6 RW 0x0 Flash clock Disable*.

1: Disable Flash clock

0: Enable Flash clock

Reserved 5:2 DC 0x0 –

Force APE FCLK Disable 1 RW 0x0 APE FCLK clock Disable*.

1: Disable APE FCLK clock

0: Enable APE FCLK clock

Force APE HCLK Disable 0 RW 0x0 APE HCLK Disable*.

1: Disable APE HCLK clock

0: Enable APE HCLK clock

Name Bits Access

Default

Value

Description

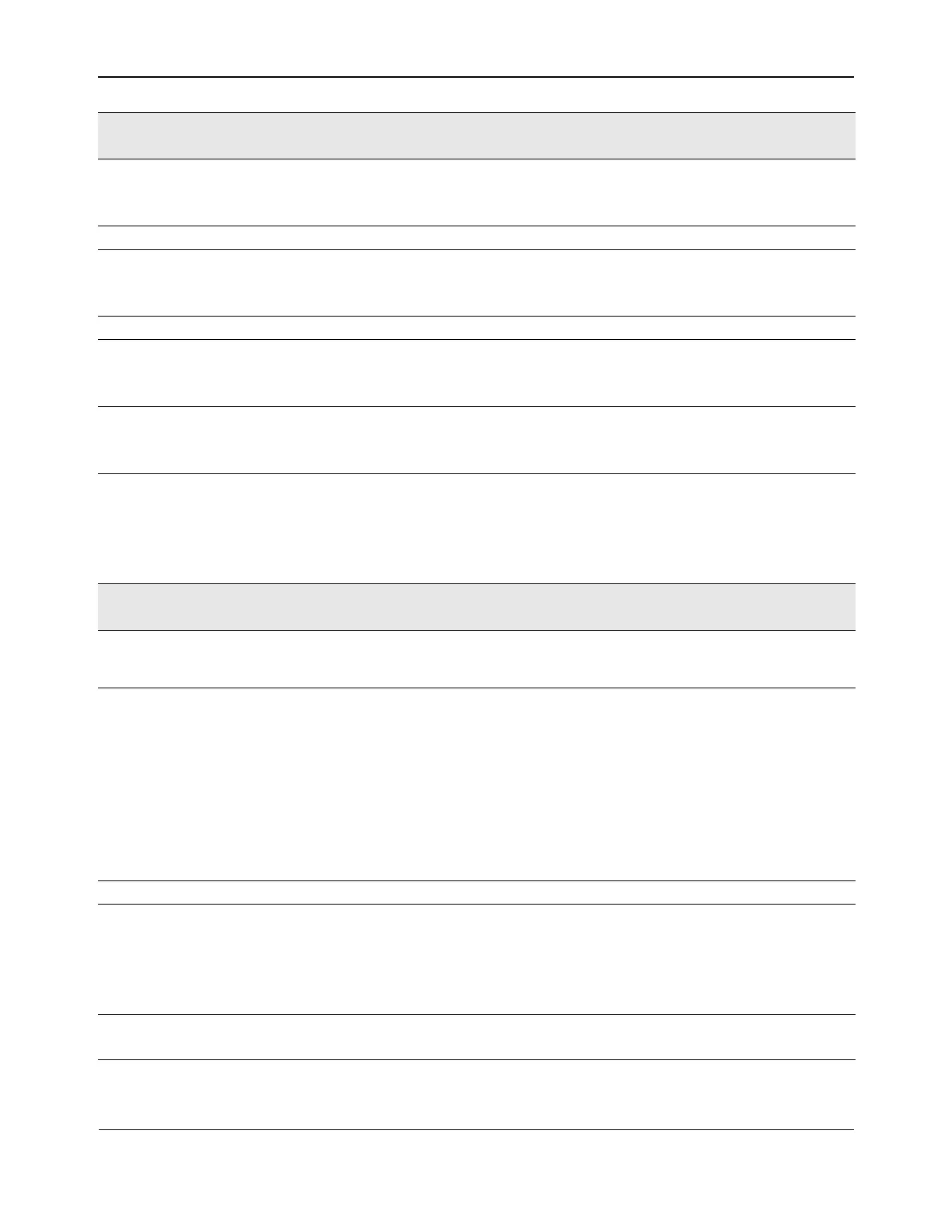

Reserved 31 RO – For 5719 four port devices, the bit31 will be used

by FUNC_NUMBER. For 5718/5720 two port

devices will not.

FUNC_NUMBER 31:30 RO 0x0 PCIE function number 1: function number

3: function 3

2: function 2

1: function 1

0: function 0

Note: CPMU port0 is tied to function 0, CPMU

port1 is tied to function1.

CPMU port2 is tied to function2.

CPMU port3 is tied to functiion3.

FUNC_ENABLE 29:25 RO – Function Enable input from System BIOS.

APE status 24:23 RO – APE Engine Status

11: Reserved

10: Deep Sleep State

01: Sleep State

00: Active State

WOL ACPI Detection Enable

Status of Port 1

22 RO – 1: ACPI detection enabled

0: ACPI detection disabled

Name Bits Access

Default

Value

Description

Loading...

Loading...