Miscellaneous Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 478

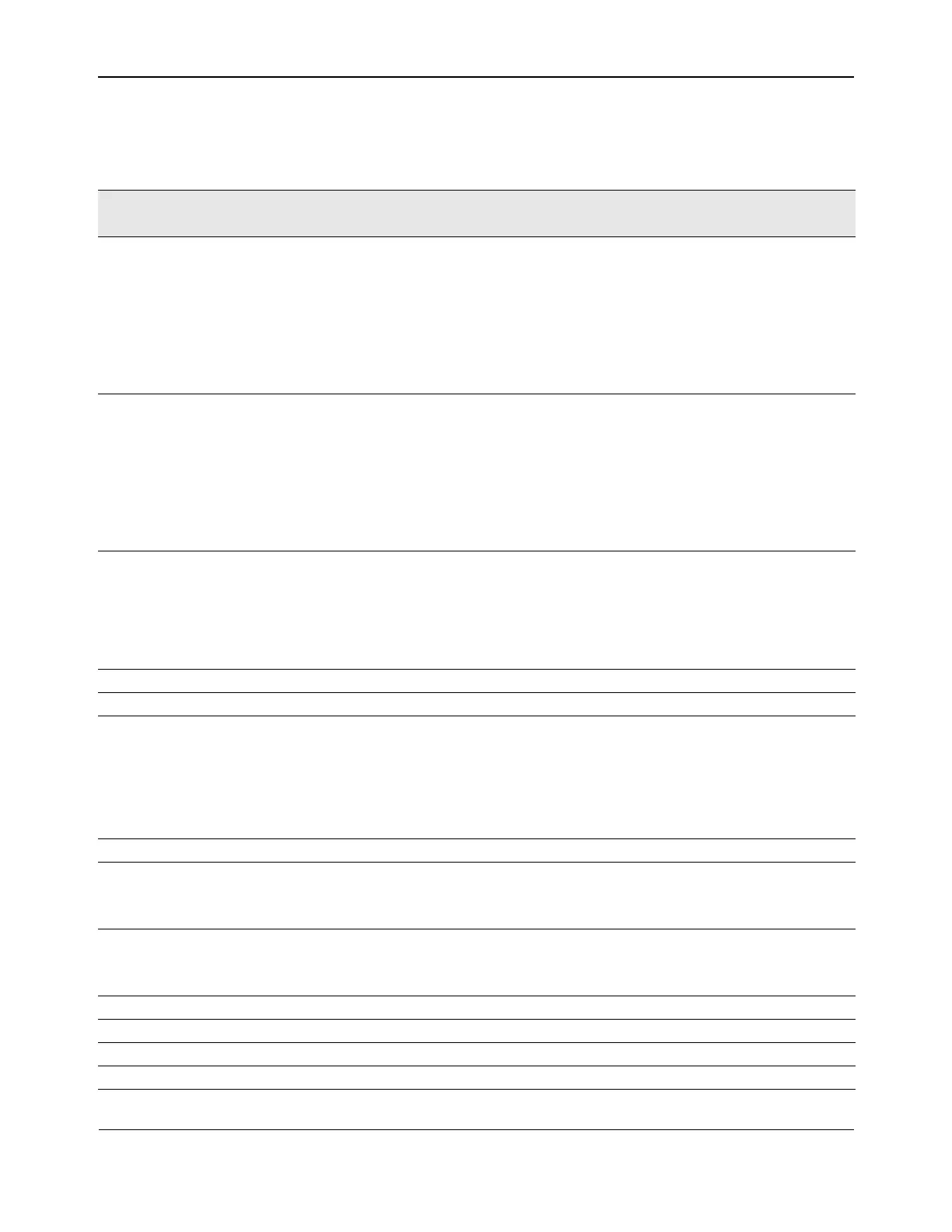

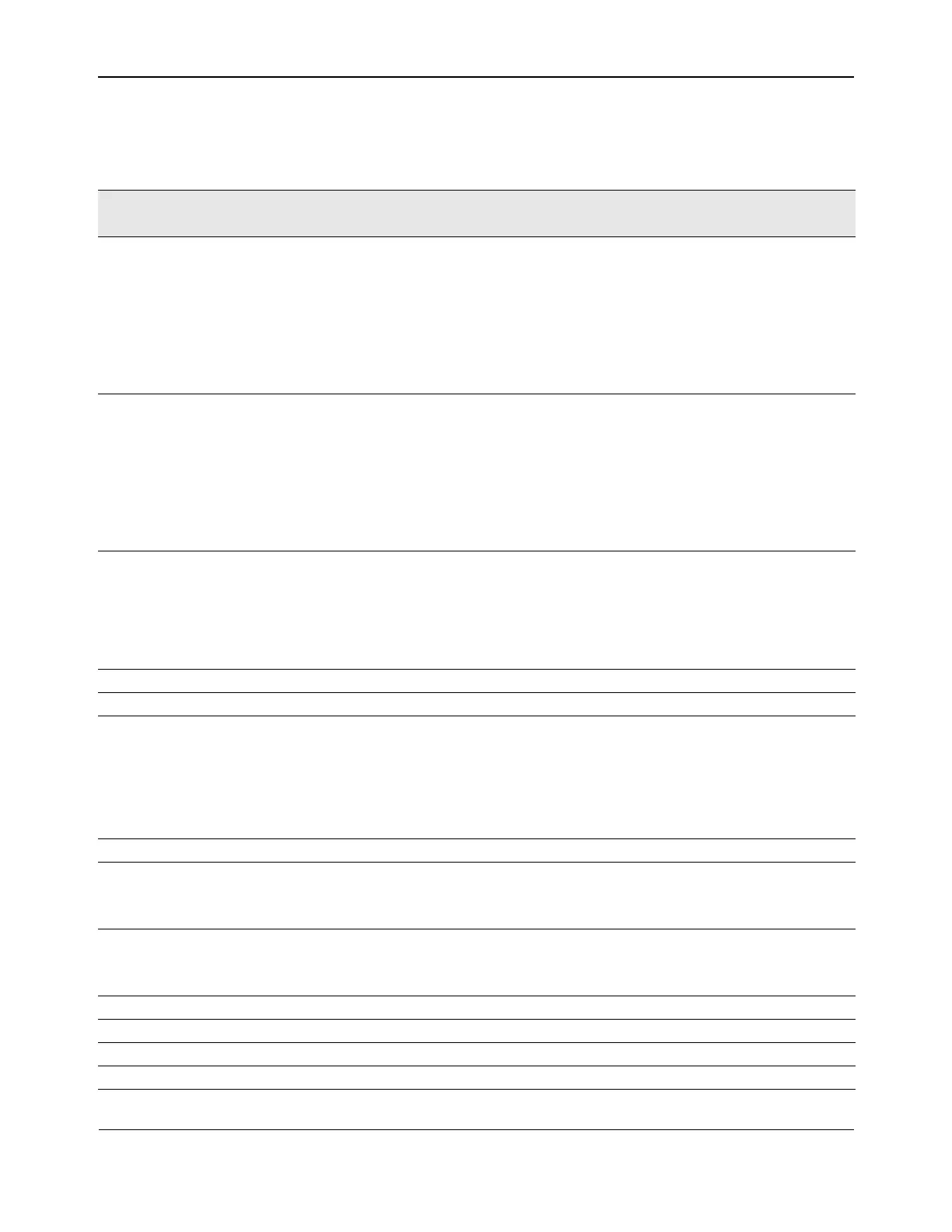

Power Management Debug Register (offset: 0x68A4)

Some of the bit in this register is initialized by hard_reset and GRC Reset.

Name Bits Access

Default

Value

Description

Powerdown Restart PCIE PLL

Enable

31 RW 0 1: Enable restart PCIE PLL when PCIE PLL is

locked up in the powerdown mode, or IDDQ

mode, or during POR, or any combinations.

0: Disable restart PCIE PLL in powerdown mode.

This bit is NOT Self-Clear. Software need to

generate a pulse by writing a 1 followed by 0 in

order to restart the PLL.

It's for debug purpose.

Normal Restart PCIE PLL

Enable

30 RW 0 1: Enable restart PCIE PLL in normal mode.

Firmware needs to write 1 and then write 0 to

restart it (pulse restart).

0: Disable restart PCIE PLL in normal mode.

This bit is NOT Self-Clear. Software need to

generate a pulse by writing a 1 followed by 0 in

order to restart the PLL.

It's for debugging purposes.

Select Core Clock Override 29 RW 0 1: Enable switching of core clock to be used for

PCIE block clocks.

0: Disable switching of core clock to be used for

PCIE block clocks.

This bit is the same as bit 16 in the PCIE Data

Link Layer Register 0x7D00.

Reserved 28:18 RO 0 –

Reserved 17 RW 0 –

PERST Override 16 RW 0 This bit is used to override the PERSTN so that

the internal CPU can access the PCIE register

when Perstn is asserted.

1: Override Perstn Reset

0: No Override

Reset by Hard Reset

Reserved 15:10 RO 0 –

irefselo 9 RO X PCIE Reference Select.

0: PCIE 100 MHz Reference Clock

1: Local 25 MHz Crystal

irxFastAcq 8 RO X PCIE PLL Fast Acquisition Select.

0: Disable Fast Acquisition

1: Enable Fast Acquisition

irxSeqStart 7 RO X PCIE RX Sequence Start

ipllSeqStart 6 RO X PCIE PLL Sequence Start

irxpowerdown 5 RO X RX Power Down Status

itxpowerdown 4 RO X TX Power Down Status

Loading...

Loading...