PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 289

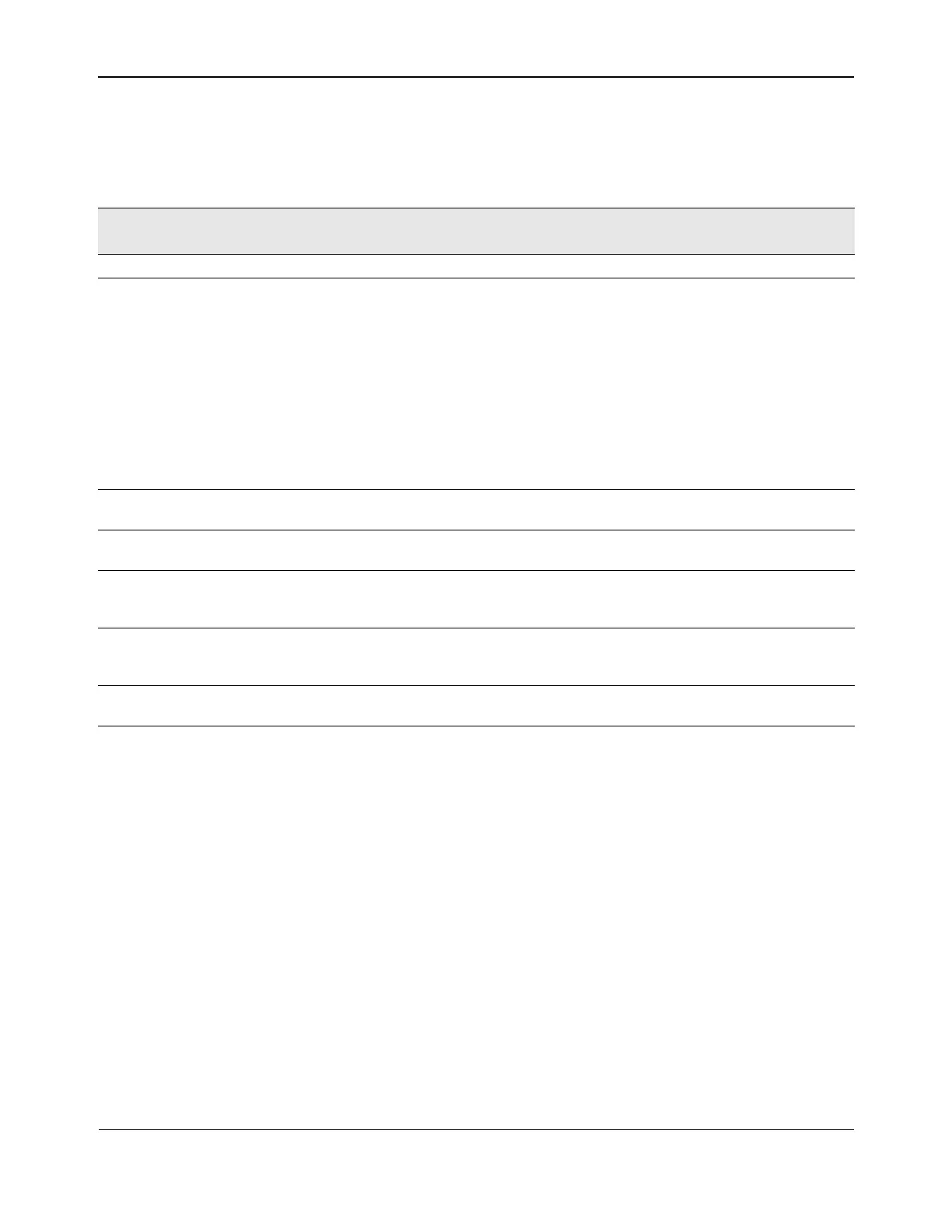

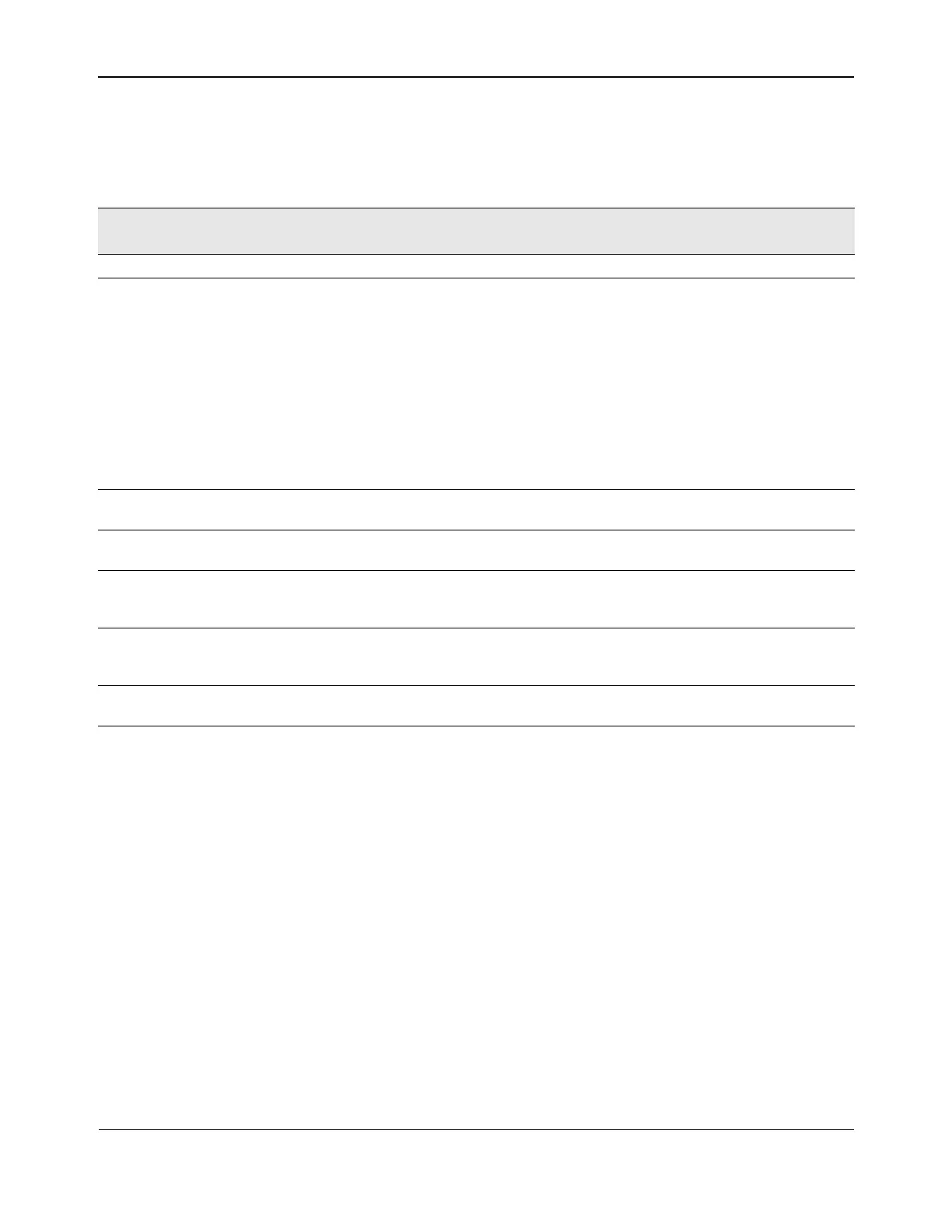

PCIe Capabilities Registers

PCIE_CAPABILITY – 0xac

Name Bits Access

Default

Value

Description

unused0 31:30 RO 0 –

MSG_NUM 29:25 RO 0 Interrupt Message Number: Indicate which MSI/

MSI-X vector is used for the interrupt message

generated in association with any of the status bits

of this capability structure. For MSI, the value in

this register indicates the offset between the base

Message Data and the interrupt message that is

generated. For MSI-X, the value in this register

indicates which MSI-X Table entry is used to

generate the interrupt message. The entry must

be one of the first 32 entries even if the function

implements more than 32 entries.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

SLOT_IMPLEMENTED 24 RO 0 Slot Implemented. This register is not supported.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

TYPE 23:20 RO 0 Slot Implemented. This register is not supported.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

VER 19:16 RO 0x2 Capability Version. PCI Express Capability

structure version number. These bits are

hardwired to 2h. Path= cfg_defs

PCIE_NEXT_CAP_PTR 15:8 RO 0 This registers contains the pointer to the next PCI

capability structure.

Path= i_cfg_func.i_cfg_public.i_cfg_rd_mux

PCIE_CAP_ID 7:0 RO 0x10 This register contains the PCIExpress Capability

ID. Path= i_cfg_func.i_cfg_public.i_cfg_rd_mux

Loading...

Loading...