MSI-X PlumbingBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 260

End of Receive Stream Interrupt

A new kind of forced interrupt is being introduced in the BCM5718 family. The End of Rx Stream Interrupt

attempts to sense the end of a receive burst and, if it does, it fires an interrupt/MSI-X instantaneously.

After completing the DMA of every Return BD to the host memory, a hardware FSM checks if the Rx-MBUF is

empty (discounting the effects of pre-allocation). If it is empty, hardware starts counting down a count value.

While the countdown is in progress, if another Rx packet starts to pour into the Rx-MBUF, the FSM goes back

to idle. However if no other Rx packet arrives, it allows the counter to go down to zero, at which point the FSM

triggers an interrupt/MSI-X. The counter basically debounces effects of IPG or short gaps among packets within

a burst.

This feature may be enabled or disabled by a register bit. The countdown preload value is also programmable.

When enabled in conjunction with Multivector MSI-X mode, there is a programmable option to fire either

Vector#0 only or all Vectors.

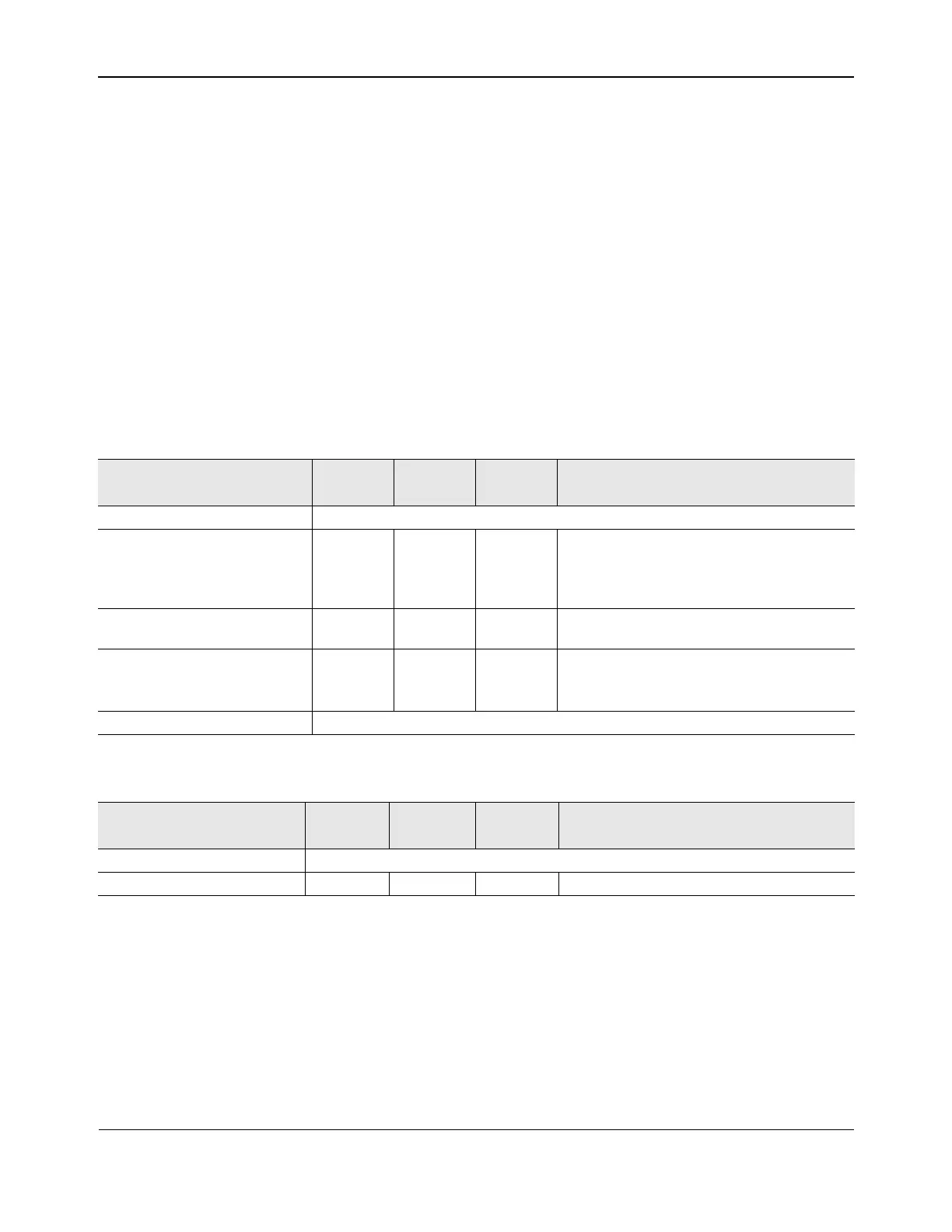

Host Coalescing Mode Register (Offset 0x3c00)

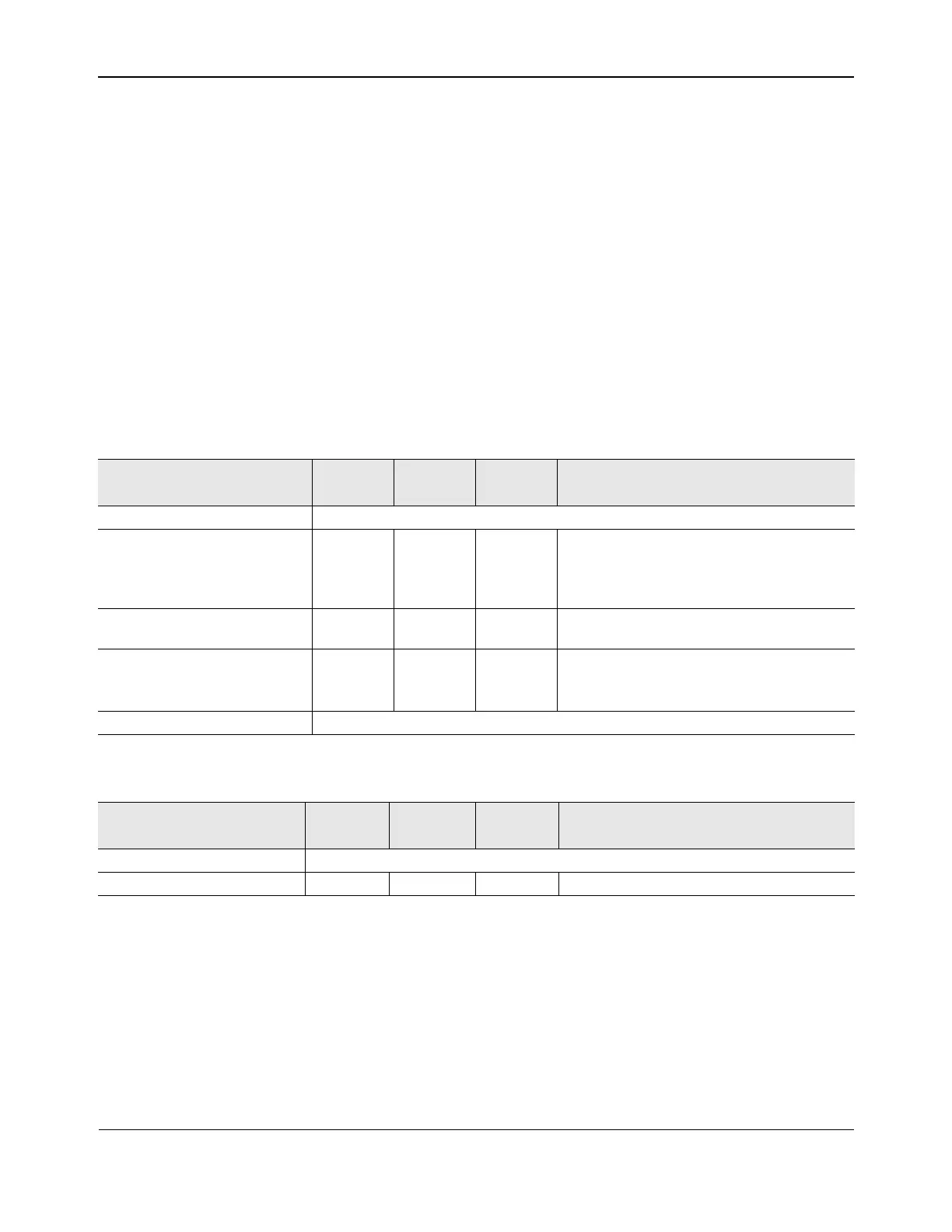

End Stream Debounce Register (Offset 0x3cd4)

Name Bits Access

Default

Value

DESCRIPTION

As defined in Legacy 31

End of Rx Stream Detector

Fires ALL MSI-X Vectors

30 RW 0x0 Write 1 to fire ALL MSI-X Vectors when an

End of Rx Stream is detected.

Write 0 to fire only MSI-X Vector#0 when an

End of Rx Stream is detected.

Enable End of Rx Stream

Interrupt

29 RW 0x0 Write 1 to enable the End of Rx Stream

Interrupt

Coalesce Now MSI-X Vector#

[16–1]

28:13 WC 0x0 Individual Coalesce Now bits associated

with MSI-X Vector# 16 through 1.

These bits are self-clearing.

As defined in Legacy 12:0

Name Bits Access

Default

Value

DESCRIPTION

As defined in Legacy 31

Reserved 30:16 RO 0 –

Loading...

Loading...