Ethernet MAC (EMAC) RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 325

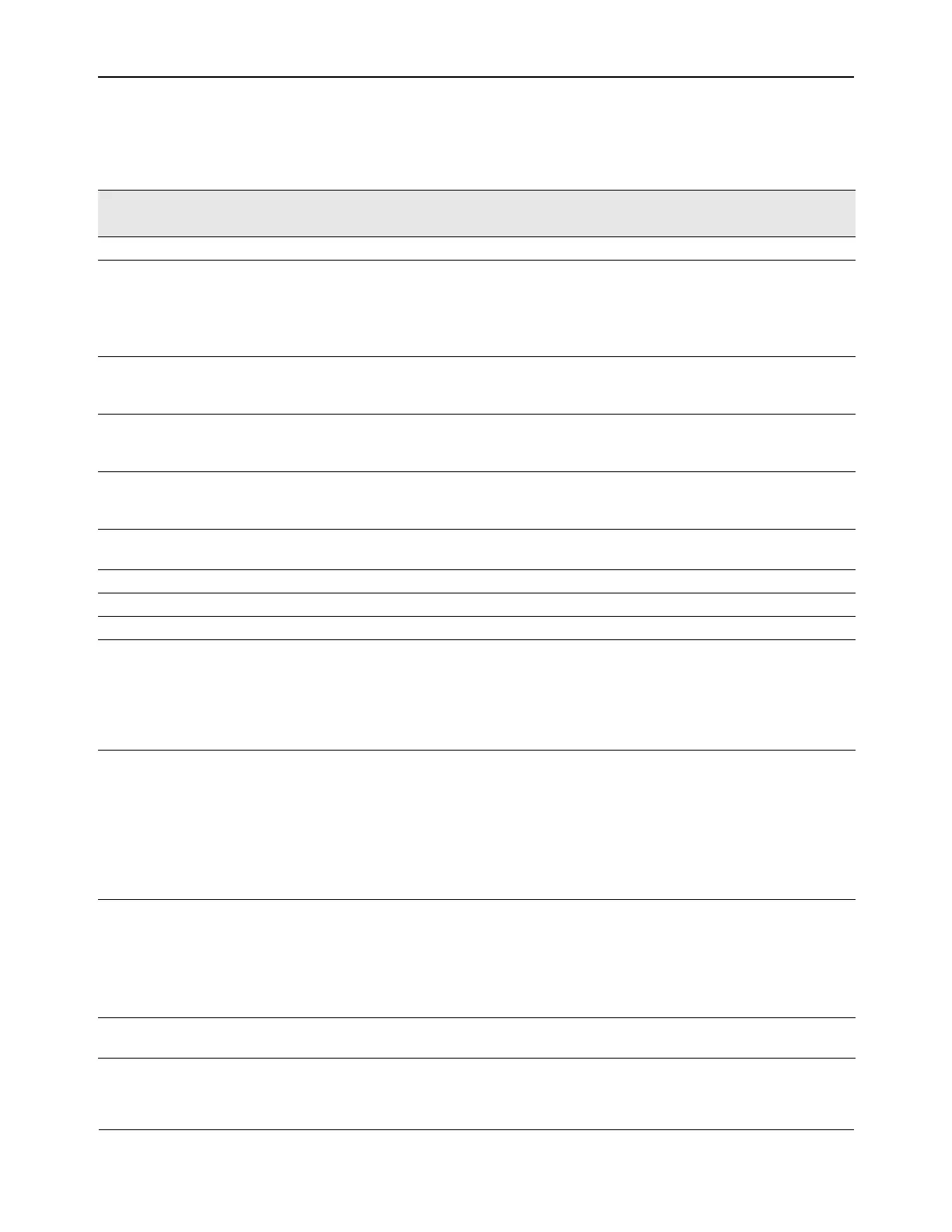

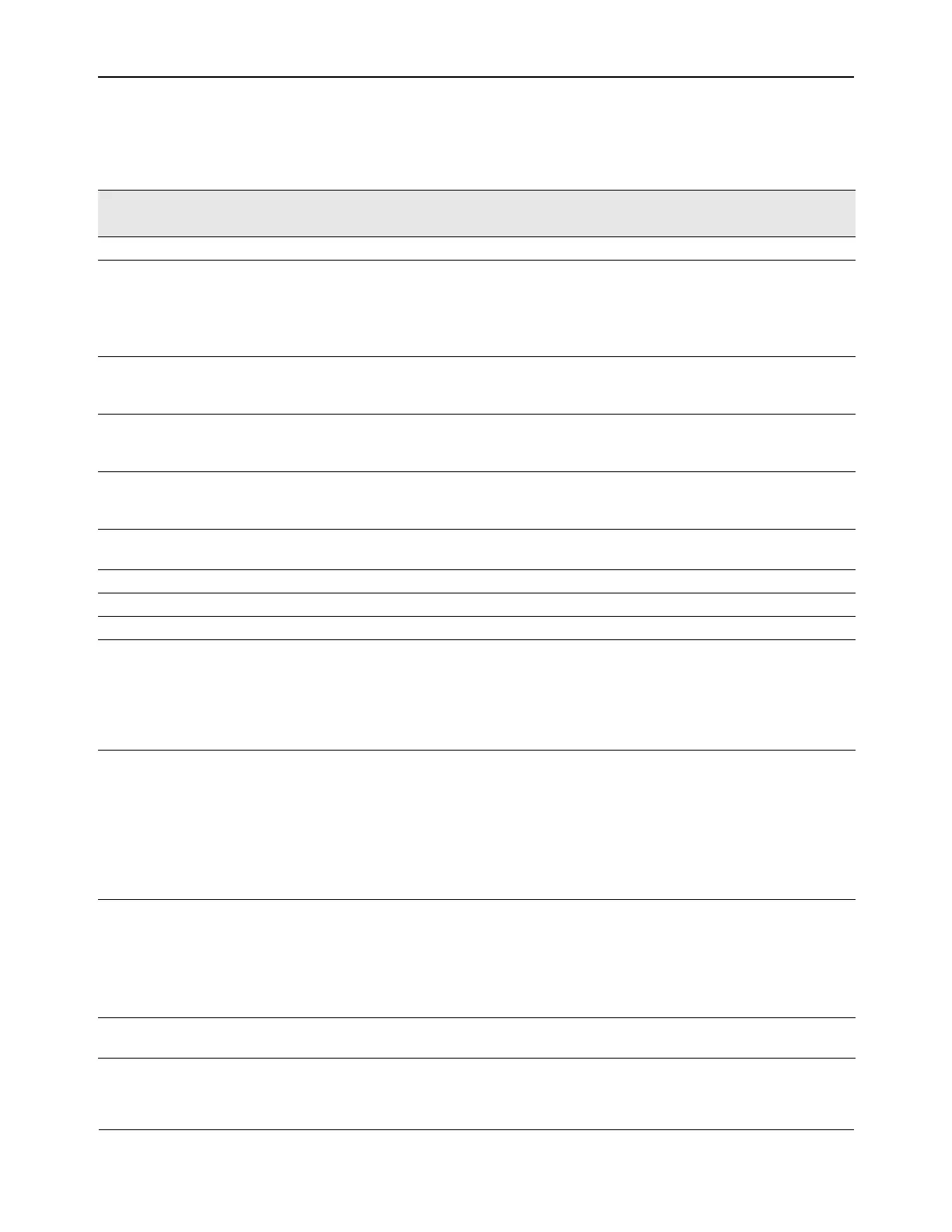

Receive Rules Control Registers (offset: 0x480 + 8*N)

The BCM5718 family employs eight receive rules (N = 0 to 7).

Name Bits Access

Default

Value

Description

Enable 31 RW 0 Corresponding Rule is enabled when set.

And With Next 30 RW 0 This rule and next must both be true to match.

The class fields must be the same.

A disabled next rule is considered true.

Processor activation bits are specified in the first

rule in series.

Activate Processor 1 29 RW 0 If the rule matches, the processor is activated in

the queue descriptor for the Receive Queue

Placement state machine.

Activate Processor 2 28 RW 0 If the rule matches, the processor is activated in

the queue descriptor for the Receive Queue

Placement state machine.

Activate Processor 3 27 RW 0 If the rule matches, the processor is activated in

the queue descriptor for the Receive Queue

Placement state machine.

Mask 26 RW 0 IF set, specifies that the value/mask field is split

into a 16-bit mask instead of a 32bit value.

Discard 25 RW 0 Discard frame if it matches the rule.

Map 24 RW 0 Use the masked value and map it to the class.

Reserved for future use 23:18 RW 0 –

Comparison Operator 17:16 RW 0 Specifies how to determine the match:

00: Equal

01: Not Equal

10: Greater Than

11: Less Than

Header Type 15:13 RW 0 Specifies which header the offset is for:

000: Start of Frame (always valid)

001: Start of IP Header (if present)

010: Start of TCP Header (if present)

011: Start of UDP Header (if present)

100: Start of Data (always valid, context

sensitive)

Class 12:8 RW 0 The class this frame is place into if the rule

matches. 0-16 where 0 means discard.

The number of valid classes is the number of

active queues divided by the Number of Interrupt

Distribution Groups.

Ring 1 has the highest priority.

Offset 7:0 RW 0 Number of bytes offset specified by the header

type.

Loading...

Loading...