10h–1Fh Register Map Detailed DescriptionBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 546

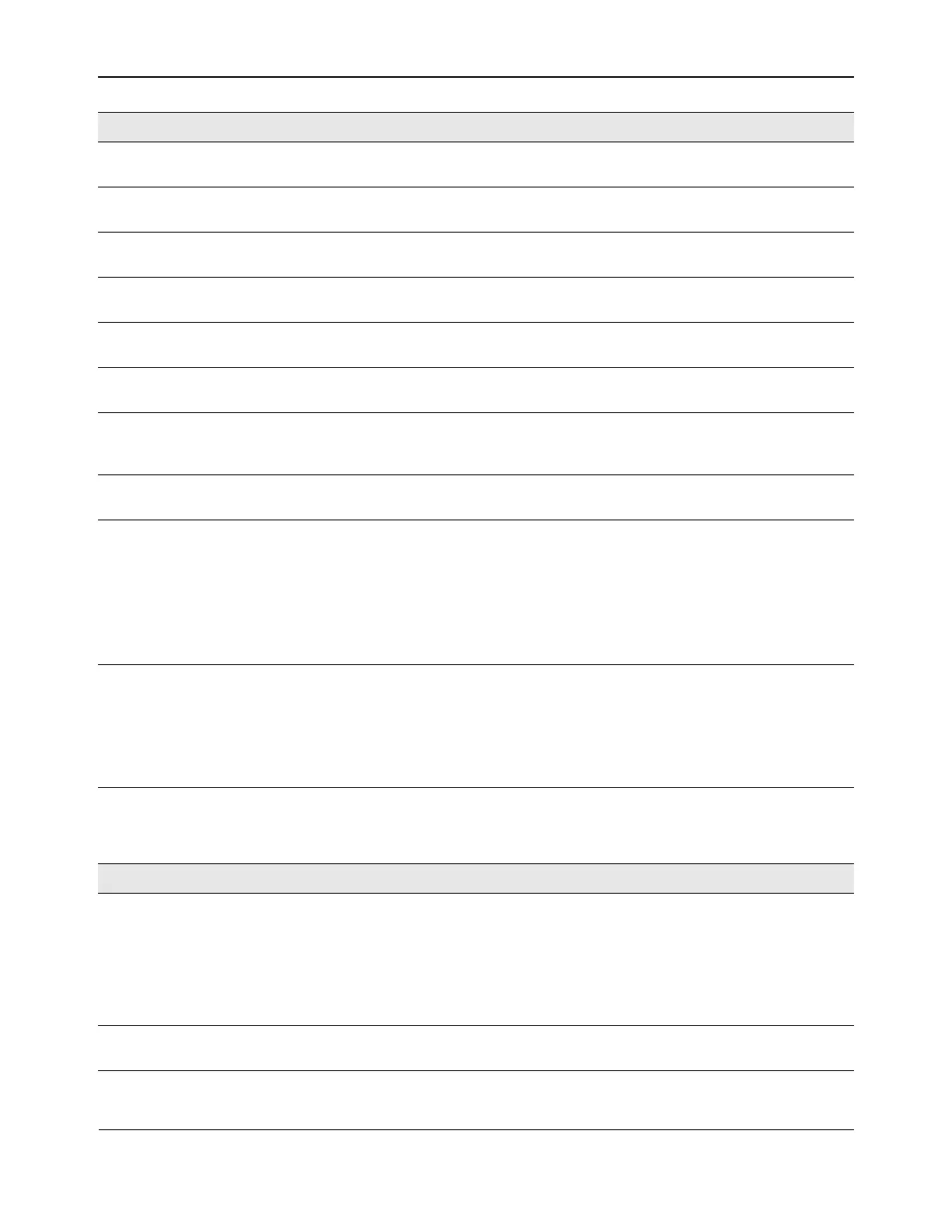

1Fh: Test2_Register

12 FORCE LINK RW 1 = force link state machine into pass state

0 = normal operation

0

11 FORCE LOCK RW 1 = force descrambler in to locked state

0 = normal operation

0

10 SCRAMBLER TEST RW 1 = speed up descrambler unlock detect timer

0 = normal operation

0

9 EXTERNAL LINK RW 1 = use tpin11 input as link status

0 = normal operation

0

8 FAST TIMERS RW 1 = timers are sped up for LSI test

0 = normal operation

0

7 MANUAL SWAP MDI

STATE

RW 1 = Swap

0 = off

0

6 RECEIVE WATCHDOG

TIMER DISABLE

RW 1 = watchdog timer disabled

0 = reset receive PMD when descrambler can’t lock within

730us of link or lock loss.

0

5 DISABLE POLARITY

ENCODE

RW 1 = disable 1000BASE-T polarity encoding

0 = normal operation

0

4 ENABLE SOFTWARE

TRIM SETTING (MAIN

DAC)

RW 1 = use software trim setting

0 = use hardware trim setting

Notes:

1) register settings from slice1, slice8 are used to control

main dac

2) register settings from slice2, slice7 are used to control

hybrid dac

0

3:0 TRIM[3:0] (MAIN DAC) RW Software trim setting

Notes:

1) only slice1, slice8 register setting are used.

2) Main dac value going to BIAS block (when enable

software trim setting = 0) is fuse_in(main

dac)+011(default)+software trim setting (main dac)

0

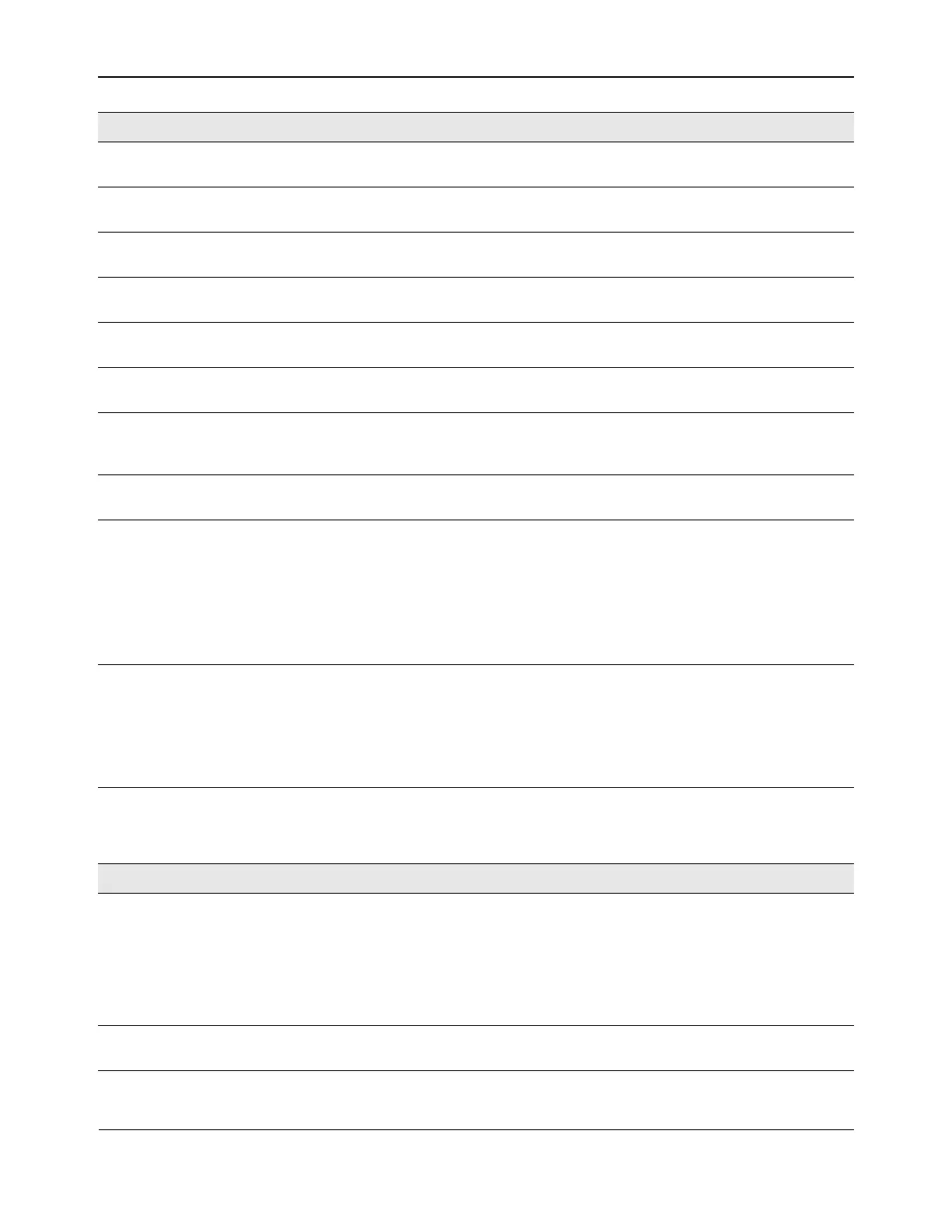

Bit Name RW Description Default

15:13 TEST SELECT AUTONEG

FSM

RW 000 = ARB

001 = RX1000

010 = RX

011 = TX1000

100 = TX

101 = BASET LINK

000

12 TEST AUTO-NEG TIMER RW 1 = auto-negotiation timer test mode

0 = normal operation

0

Bit Name RW Description Default

Loading...

Loading...