Central Power Management Unit (CPMU) RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 385

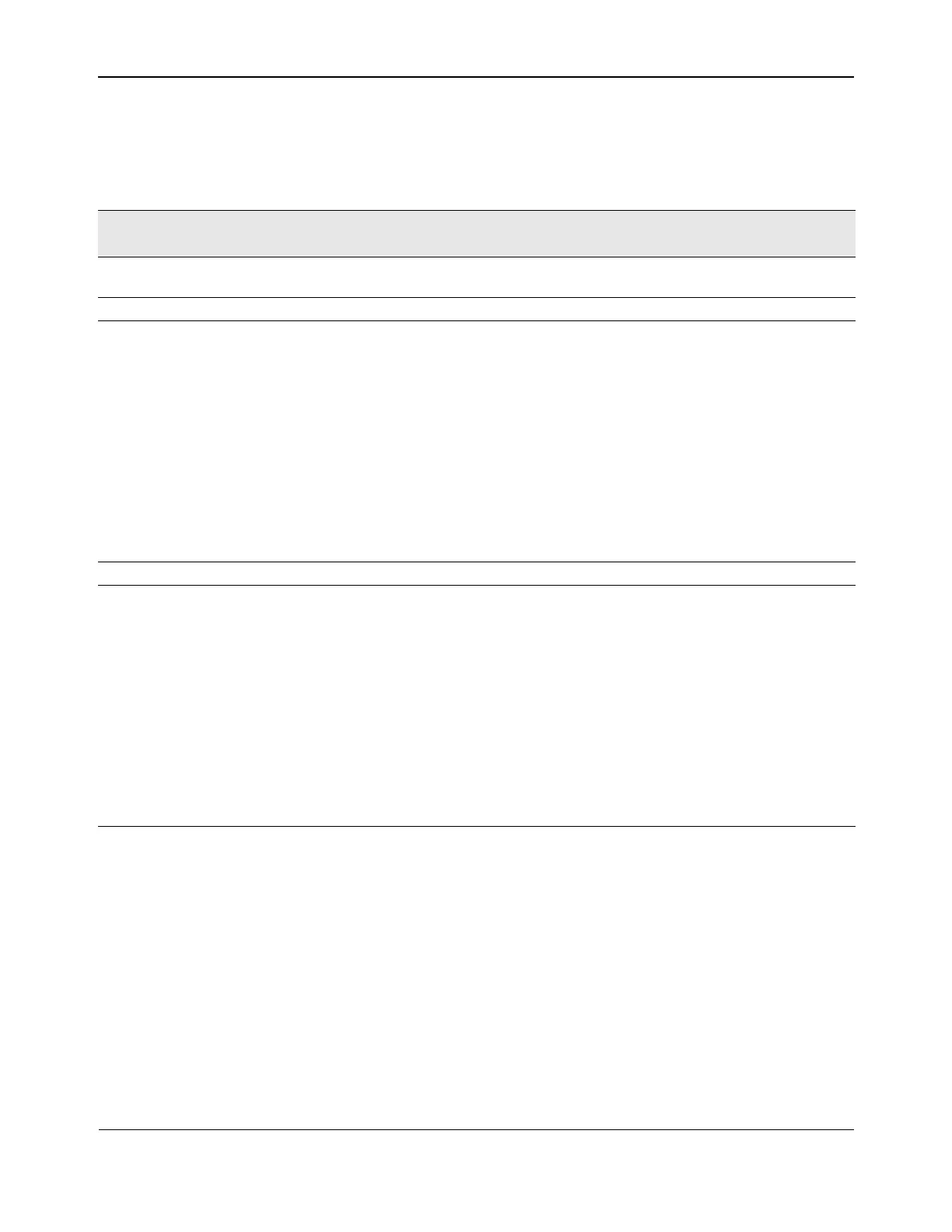

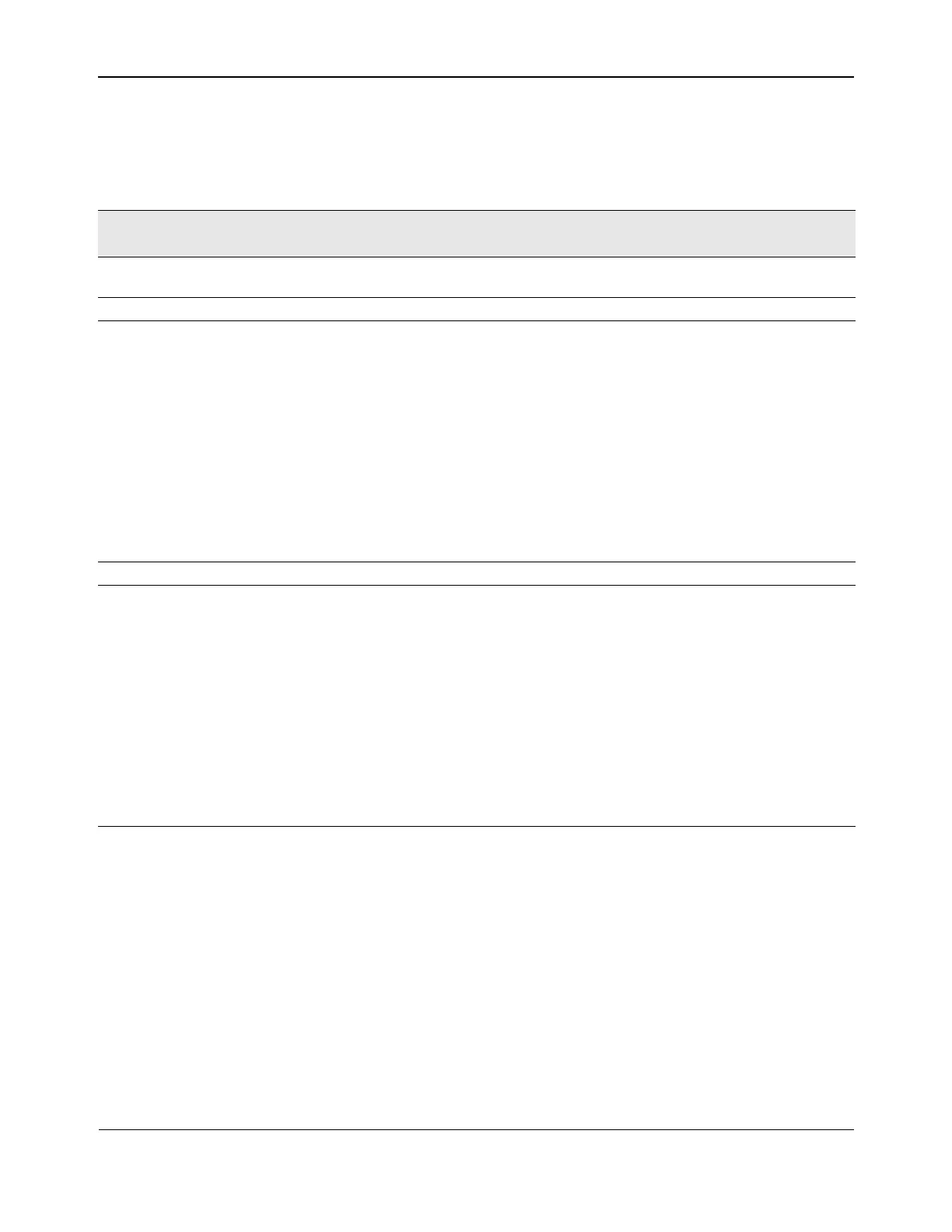

APE Sleep State Clock Policy Register (offset: 0x3620)

This register is reset by POR Reset or CPMU Register Software Reset. Please note that clocks generated by

digital frequency multiplier could be up to 3% slower than intended clock speed.

Name Bits Access

Default

Value

Description

APE Sleep HCLK Disable 31 RW 0x1 Software Controlled APE HCLK shutoff in sleep

and deep sleep state.

Reserved 30:21 DC 0x000 –

APE Deep Sleep FCLK Switch 20:16 RW 10001 Software Controlled APE Clock Speed Select.

00001: 60.0 MHz (Alt Source/2)

00011: 30.0 MHz (Alt Source/4)

00101: 15.0 MHz (Alt Source/8)

00111: 7.5 MHz (Alt Source/16)

01001: 3.75 MHz (Alt Source/32)

10001: 25.0 MHz (CK25)

10011: 12.5 MHz (CK25/2)

10101: 6.25 MHz (CK25/4)

10111: 3.125 MHz (CK25/8)

11001: 1.563 MHz (CK25/16)

Reserved 15:5 DC 0x000 –

APE Sleep FCLK Switch 4:0 RW 10001 Software Controlled APE Clock Speed Select.

00001: 60.0 MHz (Alt Source/2)

00011: 30.0 MHz (Alt Source/4)

00101: 15.0 MHz (Alt Source/8)

00111: 7.5 MHz (Alt Source/16)

01001: 3.75 MHz (Alt Source/32)

10001: 25.0 MHz (CK25)

10011: 12.5 MHz (CK25/2)

10101: 6.25 MHz (CK25/4)

10111: 3.125 MHz (CK25/8)

11001: 1.563 MHz (CK25/16)

Loading...

Loading...