PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 305

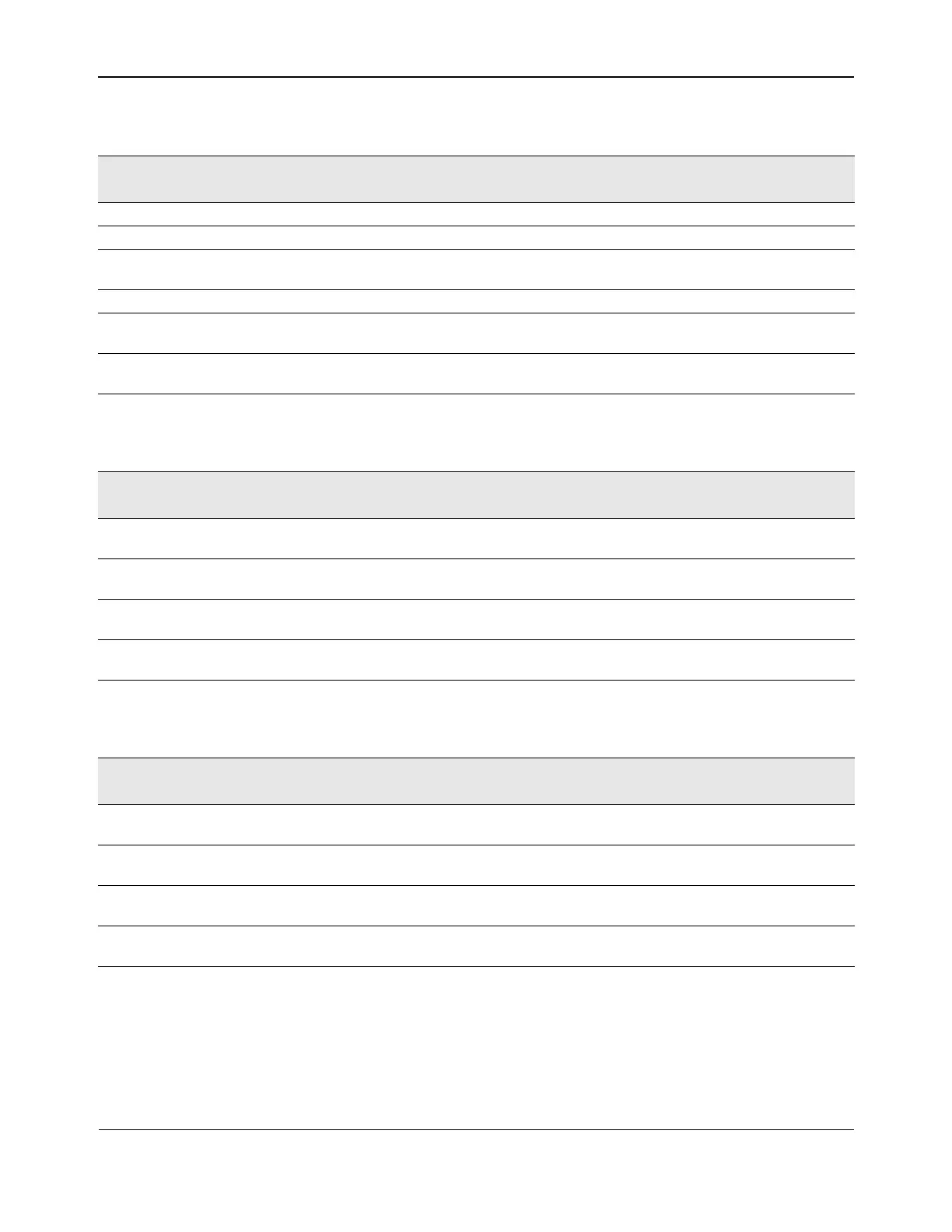

Advanced Error Capabilities and Control Register (offset: 0x118)

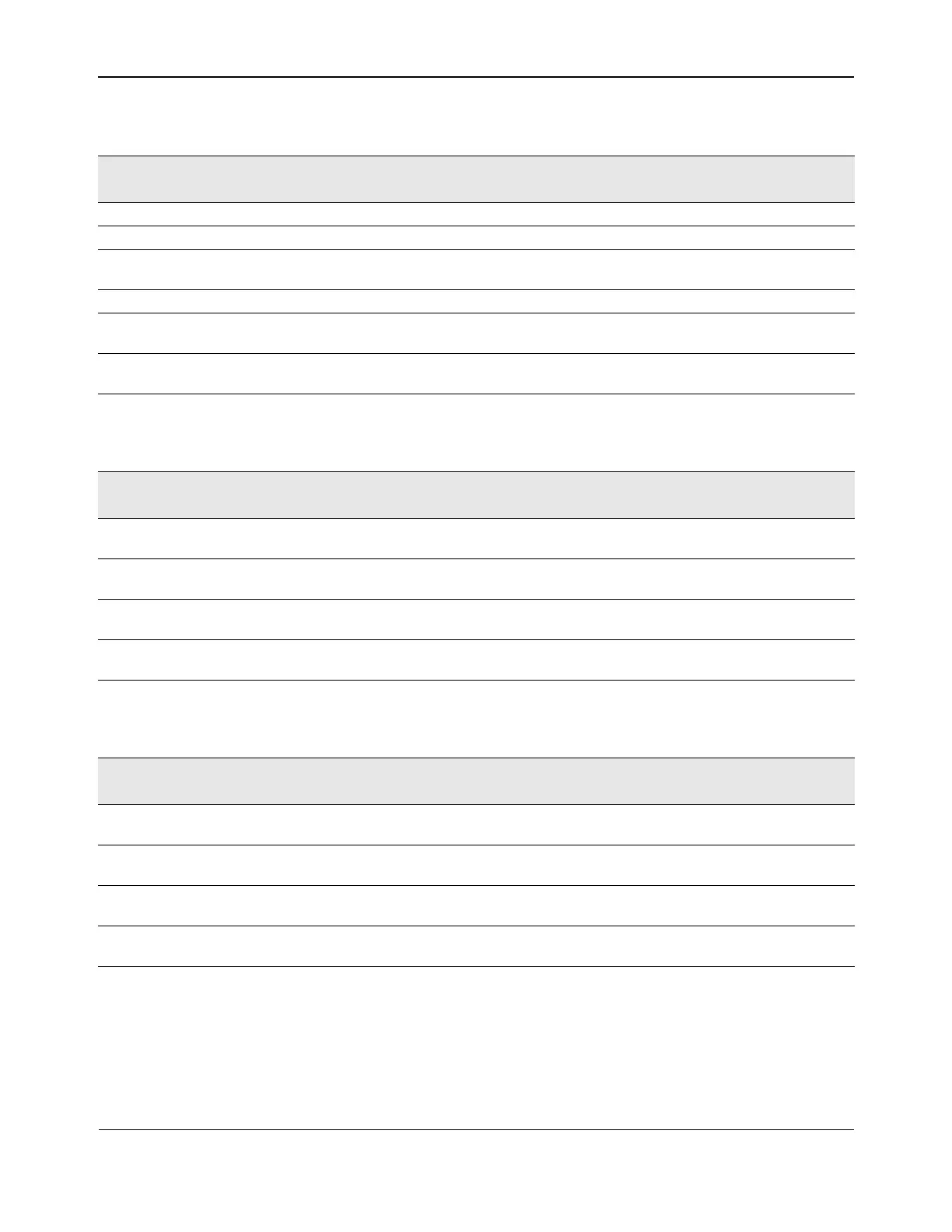

Header Log Register (offset: 0x11C)

Header Log Register (offset: 0x120)

Name Bits Access

Default

Value

Description

Reserved 31:9 RO 0 –

ECRC Check Enable 8 RWS 0 Setting this bit will enable ECRC checking.

ECRC Check Capable 7 RO 1 When this bit is set, it indicates that this device

supports ECRC checking.

ECRC Generation Enable 6 RWS 0 Setting this bit will enable ECRC generation.

ECRC Generation Capable 5 RO 1 When this bit is set, it indicates that this device

supports ECRC generation.

First Error Pointer 4:0 ROS 0 This value indicates the bit position within the

“Uncorrectable Error Status Register” 0x104.

Name Bits Access

Default

Value

Description

Header Byte 0 31:24 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 1 23:16 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 2 15:8 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 3 7:0 ROS – The TLP header of the transaction that has

incurred a failure.

Name Bits Access

Default

Value

Description

Header Byte 4 31:24 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 5 23:16 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 6 15:8 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 7 7:0 ROS – The TLP header of the transaction that has

incurred a failure.

Loading...

Loading...