DMA WriteBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 58

Buffer Manager

The buffer manager maintains pools of internal memory used by transmit and receive engines. The buffer

manager has logic blocks for allocation, free, control, and initialization of internal memory pools. The DMA read

engine requests internal memory for BDs and frame data. Figure 5 on page 57 shows the transmit data path

using the DMA Read Engine. The read DMA engine also fetches Rx BDs for the receive data path.

DMA Write

Write Engine

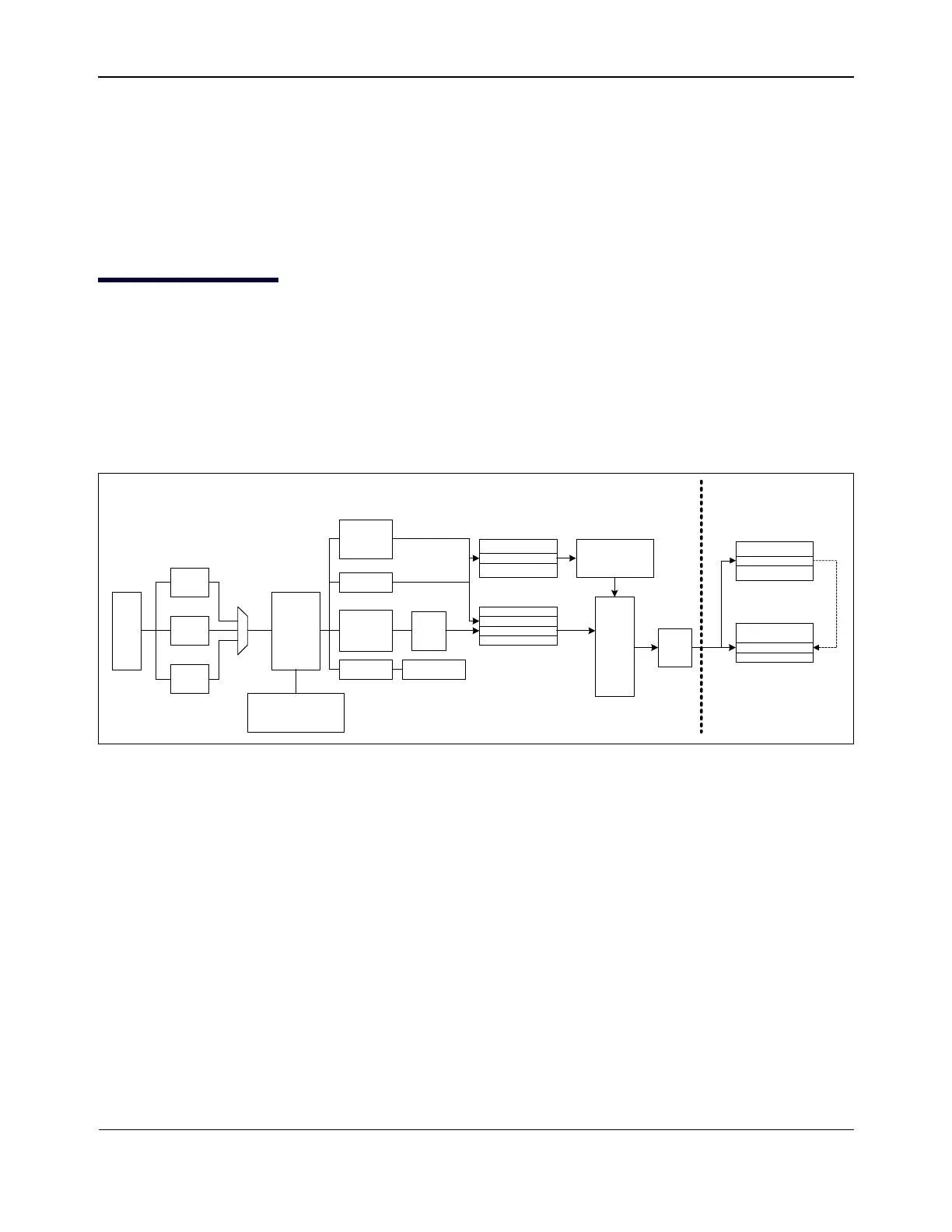

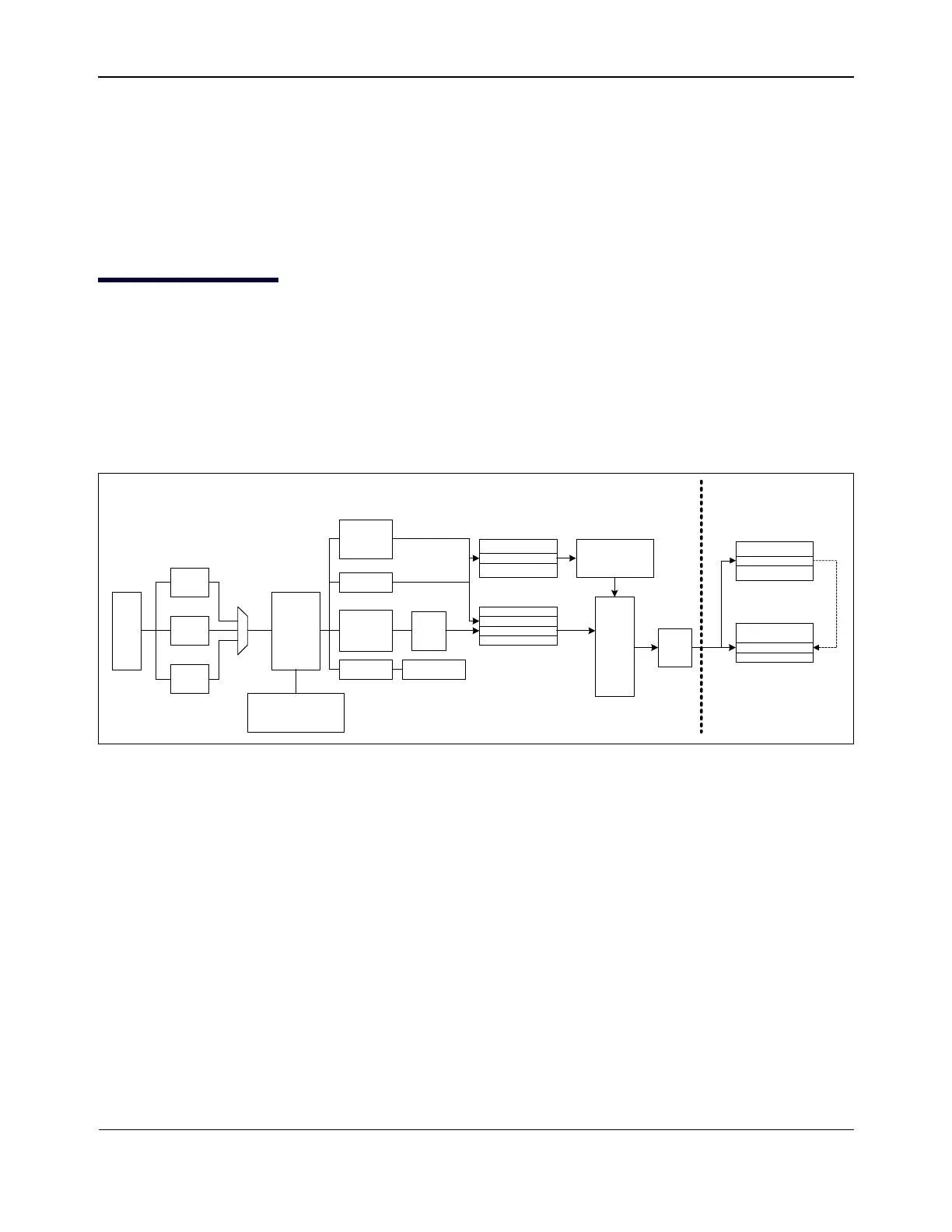

The DMA write engine, as shown in Figure 6, activates when a host write is initiated by the send or receive data

paths.

Figure 6: DMA Write Engine

The DMA write engine dequeues an internal request and performs the following functions:

• Gathers the data from device internal memory into the write DMA FIFO

• DMAs the data to the host memory from the write FIFO

• Performs byte and word swapping

• Interrupts the host using a line or message signaled interrupt

Write FIFO

The write FIFO provides elasticity during data movement from device memory to the host memory. The write

FIFO absorbs small delays created by PCIe bus arbitration. The NetXtreme family uses the write FIFO to buffer

data, so internal memory arbitration is efficient. Additionally, the FIFO isolates the PCI clock domain from the

device’s clock domain. This reduces latency on the PCI bus during the write operation (wait states are not

inserted while data is fetched from internal memory). The operation of the write DMA FIFO is transparent to host

software.

text

RX

PCS

RX

RMII

RX

GMII

RX

IO

RX

MAC

Frame

Mod

WOL

Filter

Rx

FIFO

Power

Management

Frame Header #1

Packet Data #1

Frame

Cracker

Checksum

Calculation

Rules

Checker

Statistics

BD Packet #1

NIC

BD Memory

NIC

BufferMemory

Buffer Manager

DMA

Packet Data #1

BD Packet #1

Host Receive Buffer

Descriptor Ring

Host Receive Buffer

Memory

Write

FIFO

Loading...

Loading...