TCP Segmentation Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 348

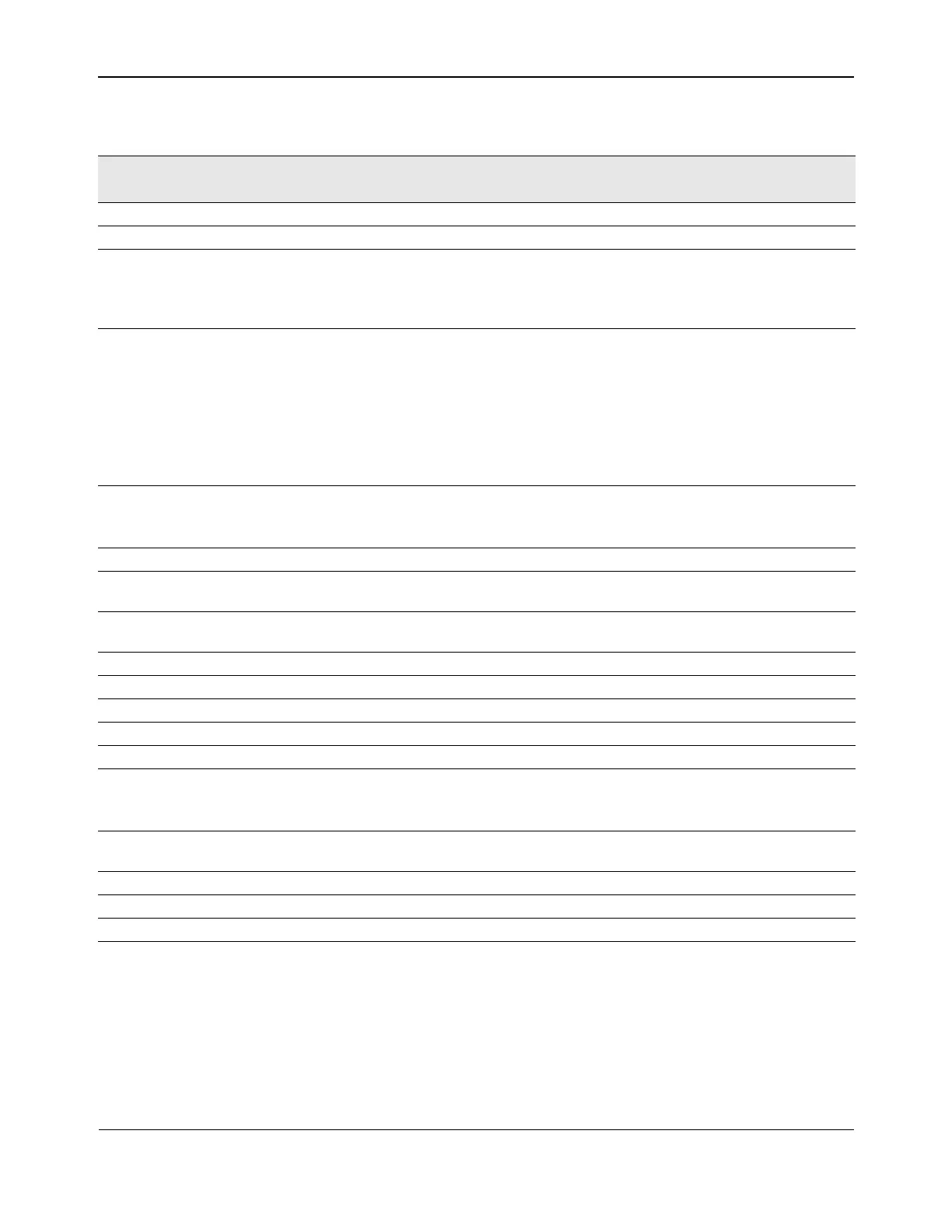

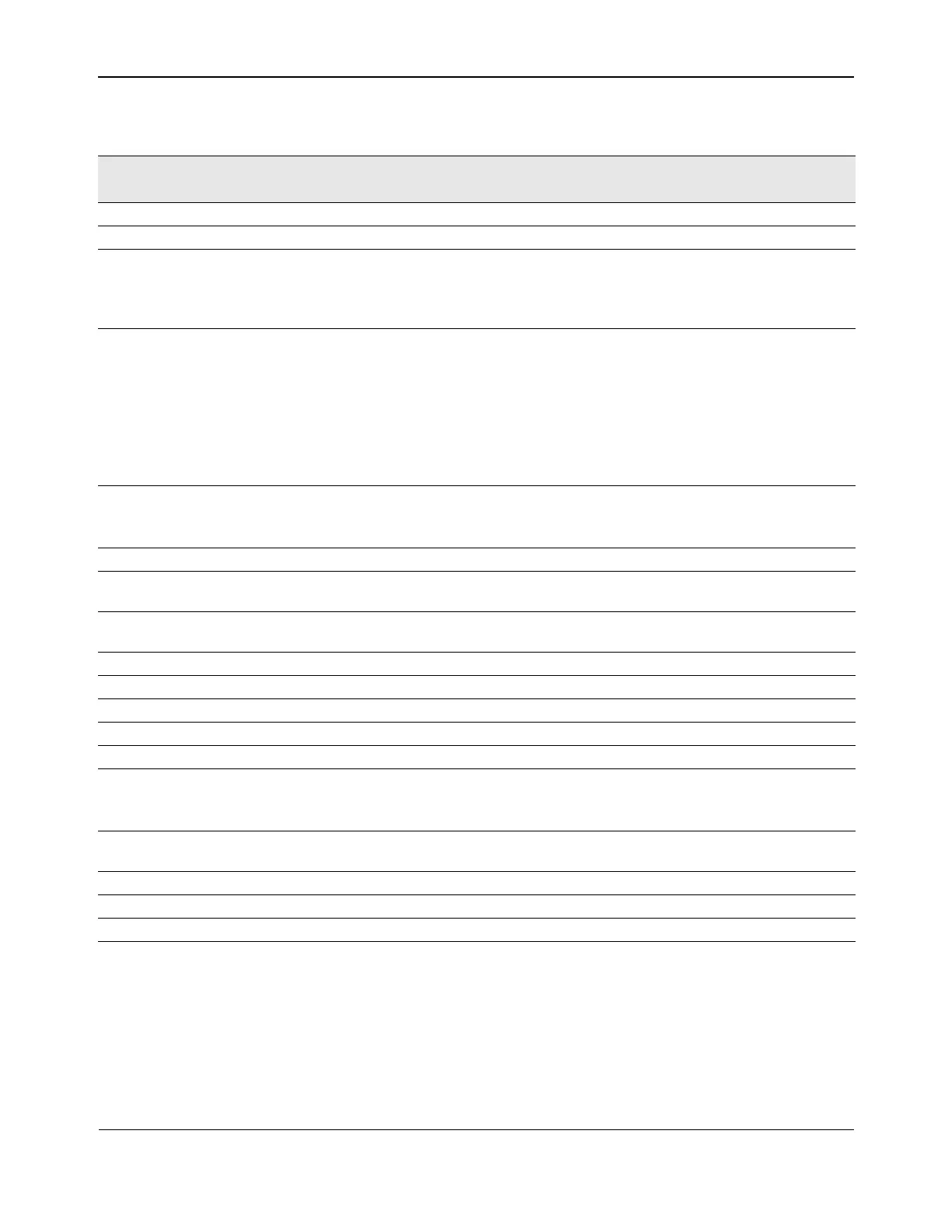

DMA Flag Register for TCP Segmentation (offset: 0xCEC)

Name Bits Access

Default

Value

Description

Reserved 31:26 RO – –

Reserved 25:20 RW – –

MBUF offset valid 19 RW – MBUF offset valid.

When this bit is set, the RDMA engine will DMA

the data into the TXMBUF starting at an offset

specified in the Length/Offset register.

Last Fragment 18 RW – Last fragment. This bit is passed transparently to

the SDC.

When this bit is set, the SDC will inform the HC

to increment the Send Ring Consumer Index.

• The bit is always set by hardware if no

firmware assisted TCP segmentation occurs.

• Otherwise, firmware sets it at the end of

fragmentation.

No Word Swap 17 RW – No Word Swap.

Set to disable endian word swap on data from

PCIE bus.

Status_dma 16 RW – –

MAC source address Select 15:14 RW – This 2-bit field determines which of the four MAC

addresses should be inserted into the frame.

MAC source address insertion 13 RW – Indicates that the predetermined source address

is inserted into the Ethernet header of the frame.

TCP/UDP checksum enable 12 RW – TCP/UDP Checksum enable.

IP Checksum enable 11 RW – IP checksum enable.

Force RAW checksum enable 10 RW – Force RAW checksum enable.

Data_only 9 RO – –

Header 8 RW – –

VLAN Tag Present 7 RW – VLAN Tag present.

Indicates that the VLAN tag should be copied to

the Frame Header by the DMA engine.

Force Interrupt 6 RW – Following the completion of this DMA, a host

interrupt is generated.

Last BD in Frame 5 RW – Last BD in frame.

Coalesce Now 4 RW – Pass through Send Buffer Descriptor flag.

mbuf 3 RW – –

Loading...

Loading...