VRQ Mapper RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 458

VRQ Enable Register (Offset 0x560)

This register contains an 18-bit field to provide the ability to enable or disable desired number of VRQs.

RX Mail Box Registers for VRQ

A set of new High Priority Mail Box Registers are introduced. The register addresses are as shown in the table

below:

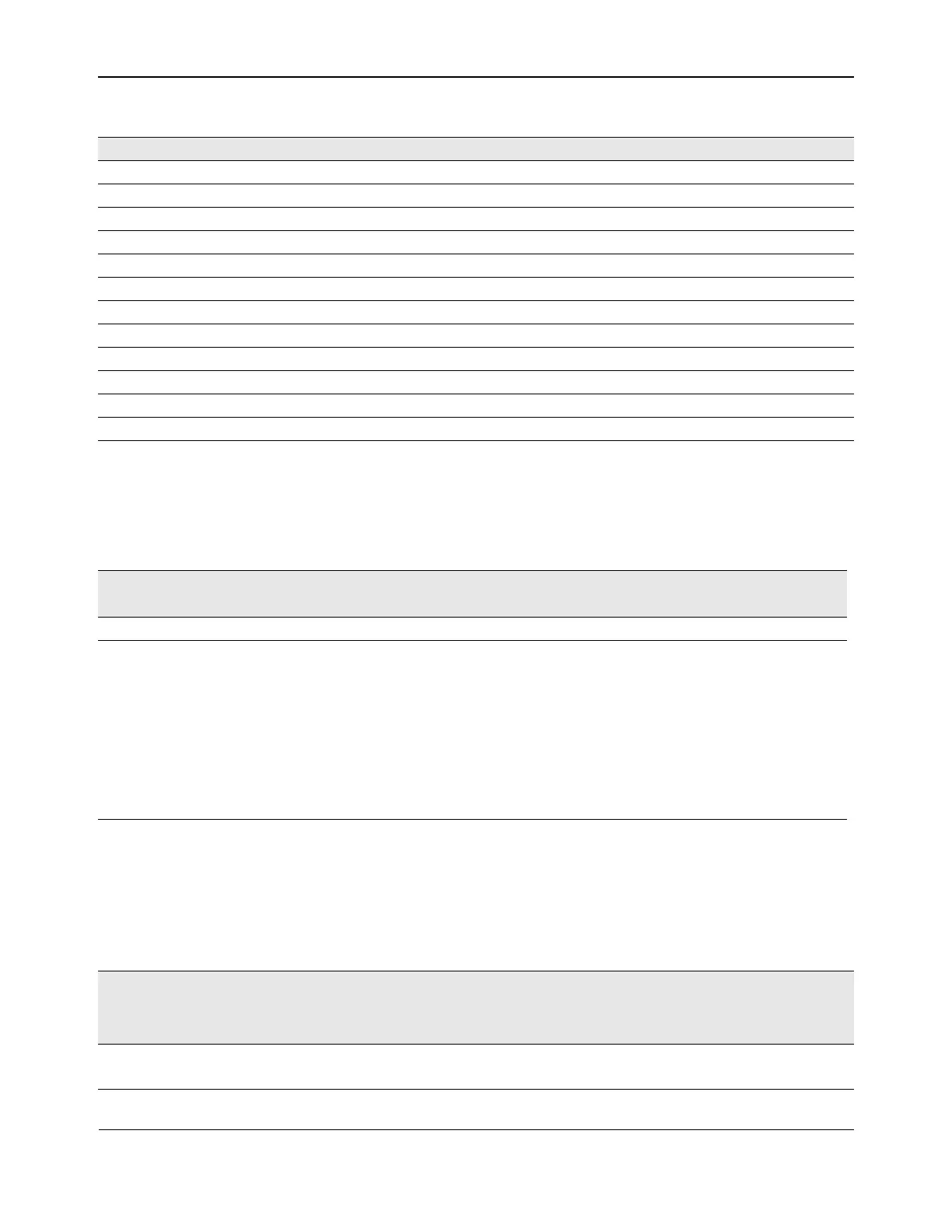

6 0x5634 0x5630

7 0x563C 0x5638

8 0x5644 0x5640

9 0x564C 0x5648

10 0x5654 0x5650

11 0x565C 0x5658

12 0x5664 0x5660

13 0x566C 0x5668

14 0x5674 0x5670

15 0x567C 0x5678

16 0x5684 0x5680

17 (Drop) 0x568C 0x5688

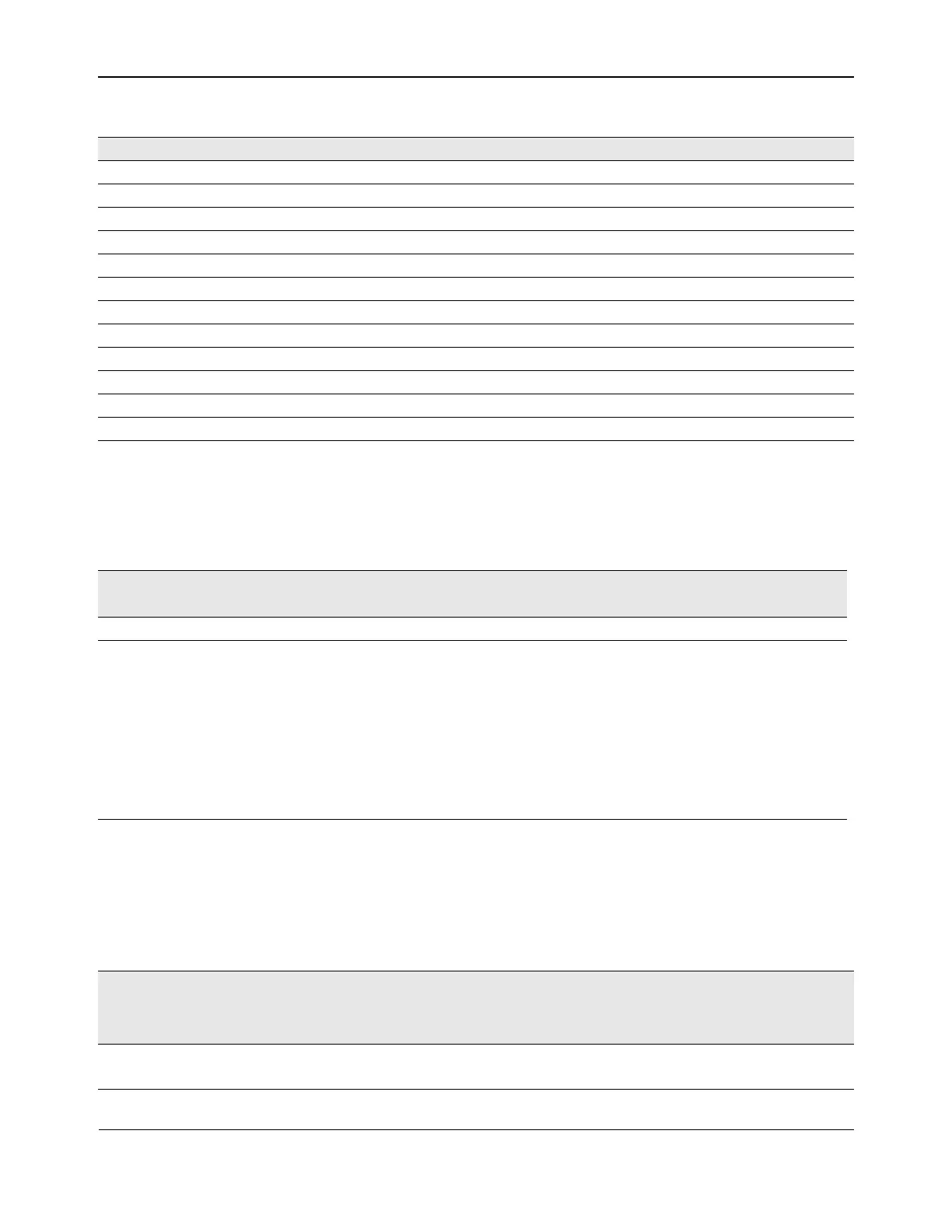

Table 115: VRQ Enable Register (Offset 0x560)

Name Bits Access

Default

Value

Description

Reserved 31:18 RO 000 Reserved

VRQ Enable Bit-Map 17:0 RW 0x0000 When a bit position is written 1 the respective

VRQ# is enabled and is capable of receiving

packets.

When a bit position is written 0, the respective

VRQ# is not capable of receiving packets – even

though its VRQ Mapper Entry is programmed.

Bit[0] => Default VRQ

Bit[16:1] => Generic VRQs

Bit[17] => Drop Queue

Table 116: High Priority Mail Box Registers for VRQ Rings

VRQ #

RX Jumbo

Ring Producer

Index

RX Standard

Ring Producer

Index

RX Return Ring

Consumer Index

Comments

NIC Diagnostic

RX Return Ring

Producer Index

0

(Default)

0x270 UNDI – 0x98

HP – 0x268

UNDI – 0x88

HP – 0x280

64-bit

Registers

0x3C80

Table 114: VRQ Mapper Register List (Cont.)

VRQ Entry # Second Half Register Address First Half Register Address

Loading...

Loading...