Send Data Completion Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 350

Send Data Completion Control Registers

All registers reset are core reset unless specified.

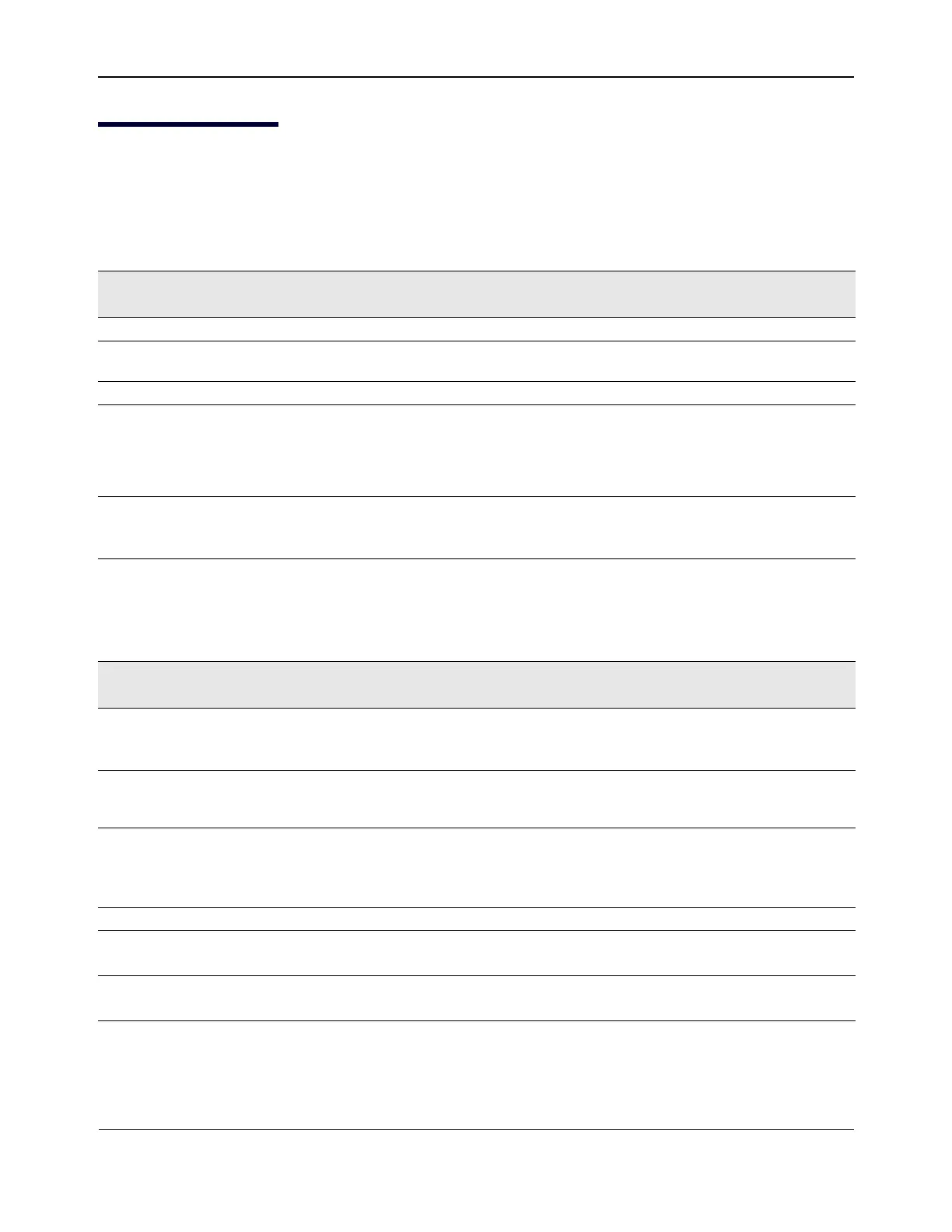

Send Data Completion Mode Register (offset: 0x1000)

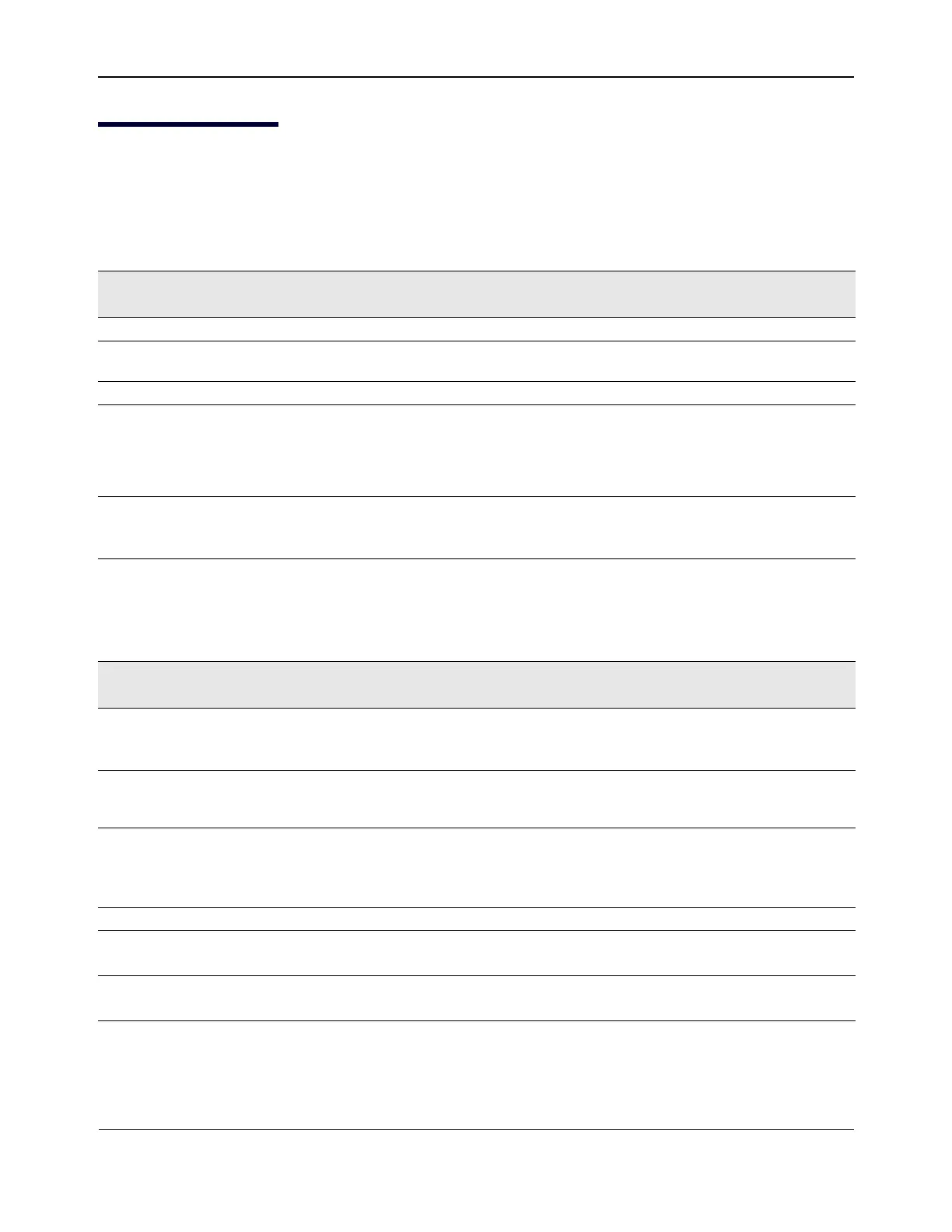

Pre-DMA Command Exchange Register for TCP Segmentation

(offset: 0x1008)

Name Bits Access

Default

Value

Description

Reserved 31:5 RO 0 –

Disable Delayed Host

Coalescing

4 RW 0 A value 1 disables the Delayed HC feature

introduced in BCM5718 family.

Reserved 3:2 RO 0 –

Enable 1 RW 1 This bit controls whether Send Data Completion

state machine is active or not. When set to 0, it

completes the current operation and cleanly

halts. Until it is completely halted, it remains one

when read.

Reset 0 RW 0 When this is set to 1, the Send Data Completion

state machine is reset.

This is a self-clearing bit.

Name Bits Access

Default

Value

Description

PASS 31 RW 1 If this bit is set to 0, the CPU will be invoked to

process TXMBUF data.

It is same as SDCQ bit 143.

SKIP 30 RW 0 CPU Sets this bit to 1 to inform the SDC that the

post-processing is completed and hardware can

resume operation.

End of Fragmentation 29 RW 1 If this bit is set to 1, SDC will request the HC to

increment Send Ring Consumer Index when

CPU sets the SKIP bit.

It is same as SDCQ bit 12.

Reserved 28:12 RO 0 –

Head TXMBUF pointer 11:6 RW 0 Head TXMBUF Pointer.

They are same as SDCQ bits 11:6.

Tail TXMBUF pointer 5:0 RW 0 Tail TXMBUF Pointer.

They are same as SDCQ bits 5:0

Loading...

Loading...