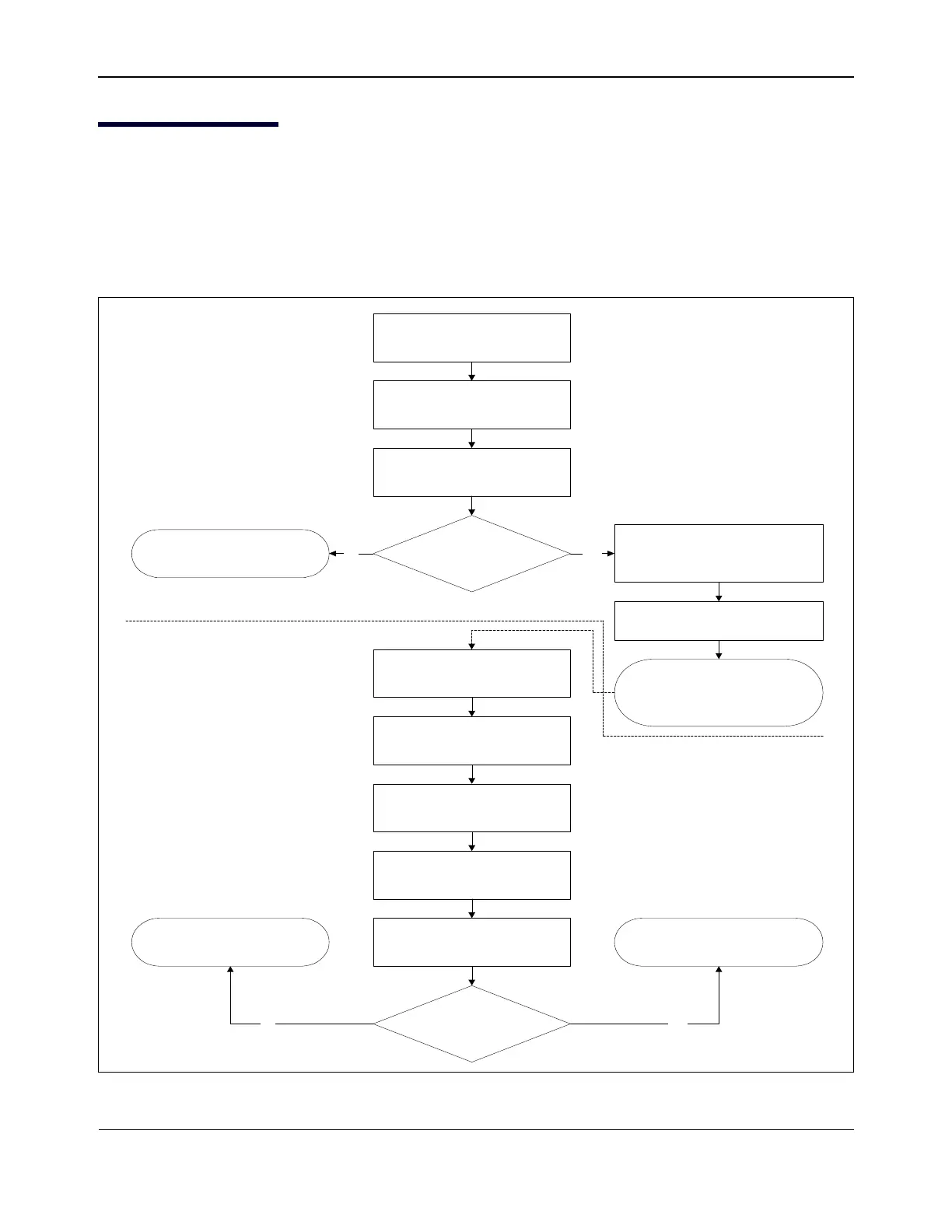

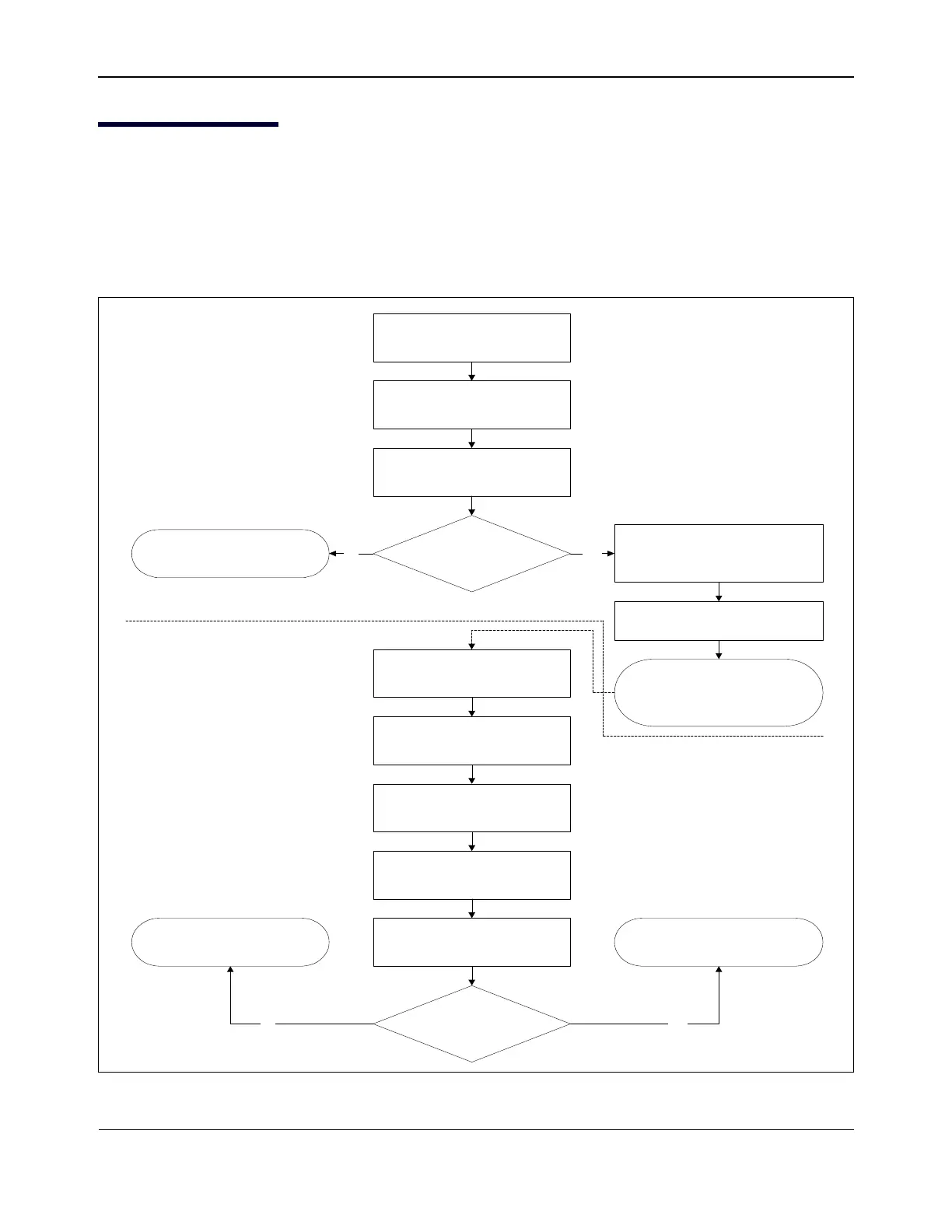

Is the "Updated bit" set in the Status

Block?

Driver reads the "status word" field in the

570X's "Status Block" (located in host

memory)

No Yes

NIC encounters an Interrupt event and

asserts in INTA# line to interrupt host

Host OS receives Interrupt and calls NIC

driver's ISR

Tell the OS "Not my interrupt", and

RETURN (this is important for interrupt-

sharing environments)

Driver claims the Interrupt and schedules a

callback to handle the interrupt processing

(many OSes due this via a lower priority

thread). Allternatively, the driver could directly

invoke the interrupt processing code.

Driver writes a value of '"1" into the 570X's

Interrupt Mailbox 0 register. While this register

contains a nonzero value, it prevents future

interrupt assertions from the 570X.

Driver clears the "updated" bit in the Status

Block.

Process any Link Status change events.

Process any received packets (receive

interrupts).

Process any completed transmits (transmit

interrupts).

Read the,

Is the "Updated bit" set in

the Status Block?

No Yes

Read Interrupt Mailbox 0 in order to flush

any posted writes in the PCI chipset.

Enable Interrupts by writing the Interrupt

Mailbox 0 register to '0'.

No more work to do. Exit the DPC

There is more work to do. Force an interrupt

by setting bit 2 in the Misc Local Control

Regsiter (offset 0x6808)

DPC Code

ISR Code

Loading...

Loading...