PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 286

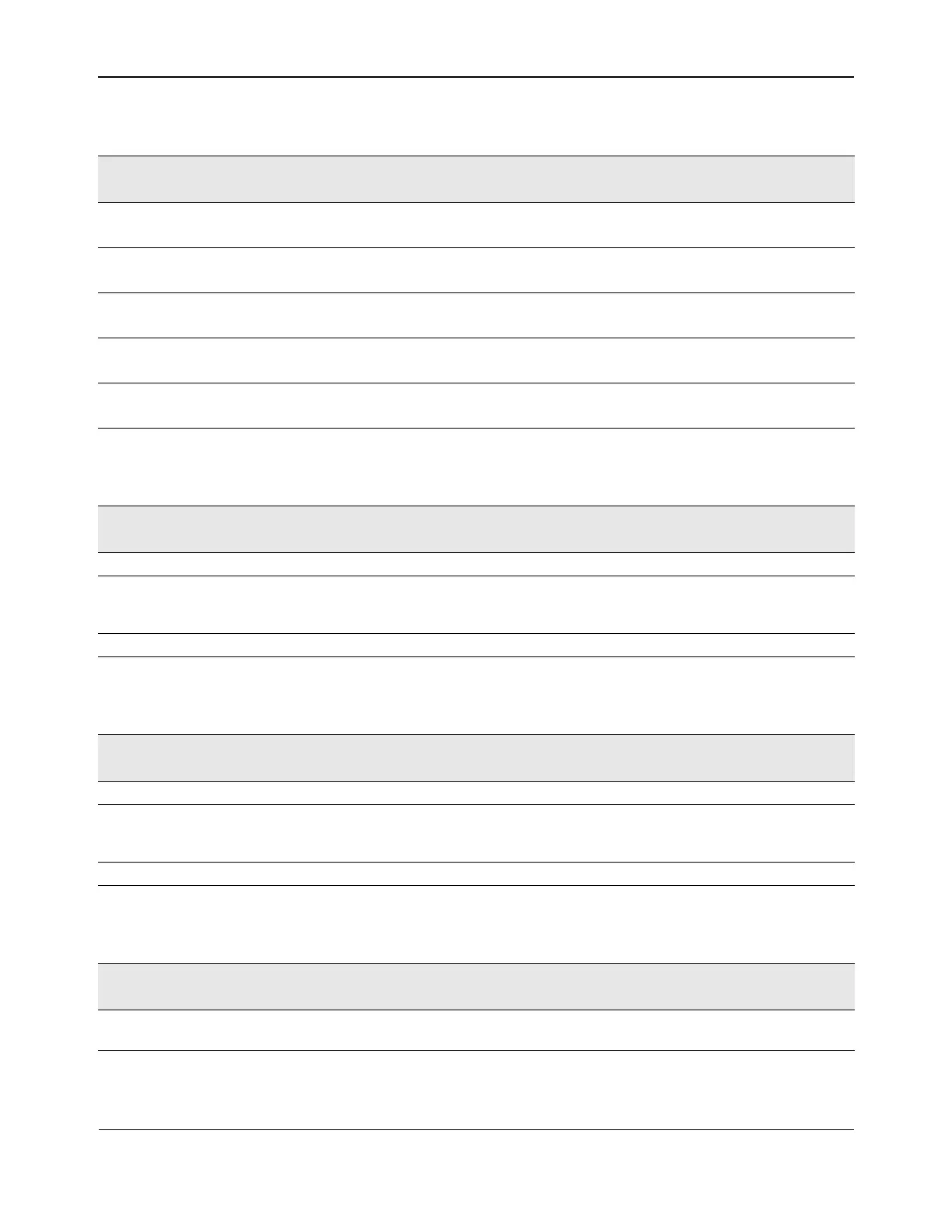

Reset Counters Initial Values Register (offset: 0x74)

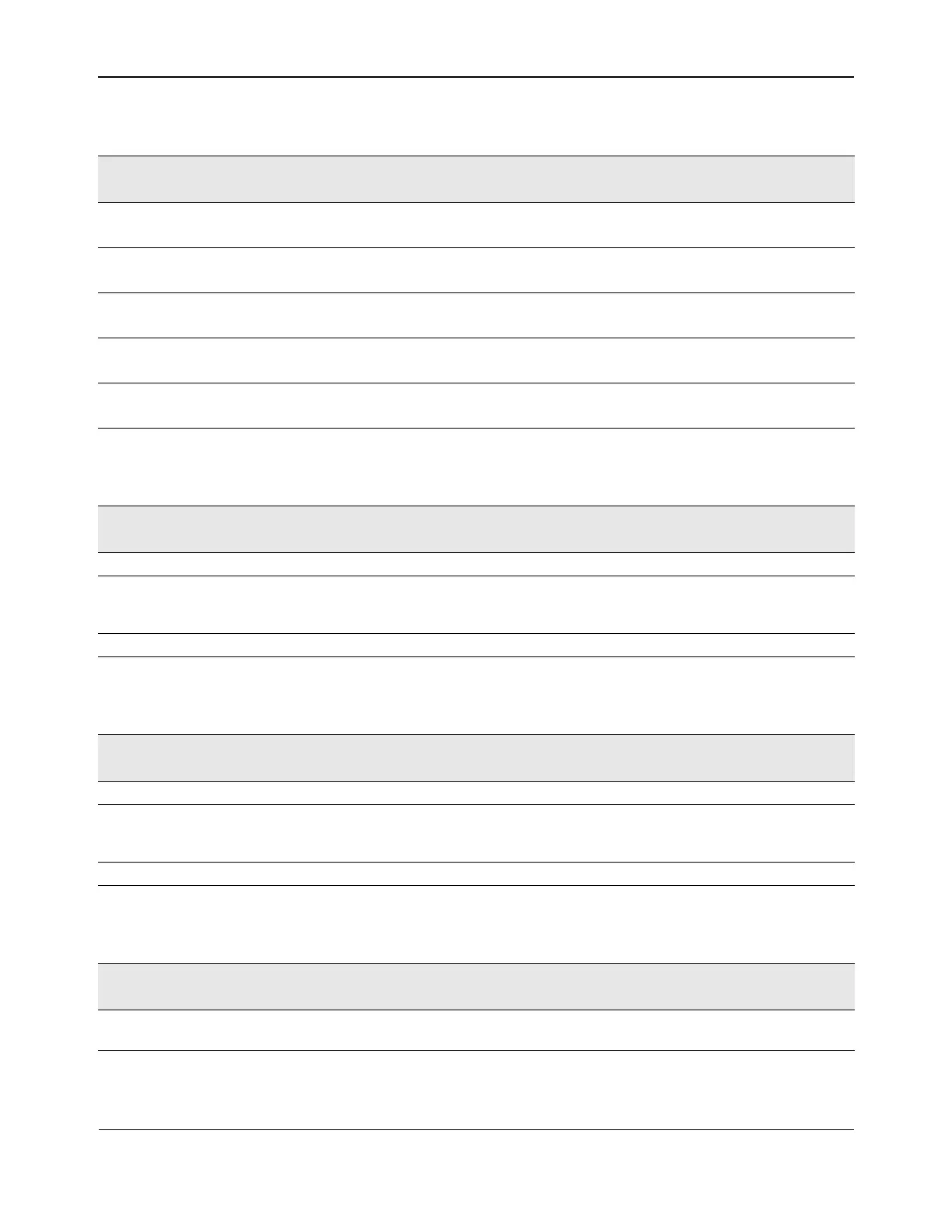

Register Base Register (offset: 0x78)

Memory Base Register (offset: 0x7C)

Register Data Register (offset: 0x80)

Name Bits Access

Default

Value

Description

Reset Counter 5 Register

(PCI CLK Core Syn Reset)

31:28 Host

RW

Any Keep tracks of the number of Core Syn Reset that

are synchronized in the PCI Clock Domain

Reset Counter 4 Register

(Hot Reset)

27:24 Host

RW

Any Keep tracks of the number of Hot Reset events.

Reset Counter 3 Register

(GRC Reset)

23:16 Host

RW

Any Keep tracks of the number of GRC Reset.

Reset Counter 2 Register

(Perst Reset)

15:8 Host

RW

Any Keep tracks of the number of Perst events.

Reset Counter 1 Register

(LinkDown Reset)

7:0 Host

RW

Any Keep tracks of the number of LinkDown Reset

events.

Name Bits Access

Default

Value

Description

Reserved 31:18 RO 0 –

Register Base Register 17:2 RW X Local controller memory address of a register than

can be written or read by writing to the register

data register

Reserved 1:0 RO 0 –

Name Bits Access

Default

Value

Description

Reserved 31:24 RO 0 –

Memory Base Register 23:2 RW X Local controller memory address of the NIC

memory region that can be accessed via Memory

Window data register

Reserved 1:0 RO 0 –

Name Bits Access

Default

Value

Description

Register Data Register 31:0 RW X Register Data at the location pointed by the

Register Base Register

Loading...

Loading...