Miscellaneous Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 479

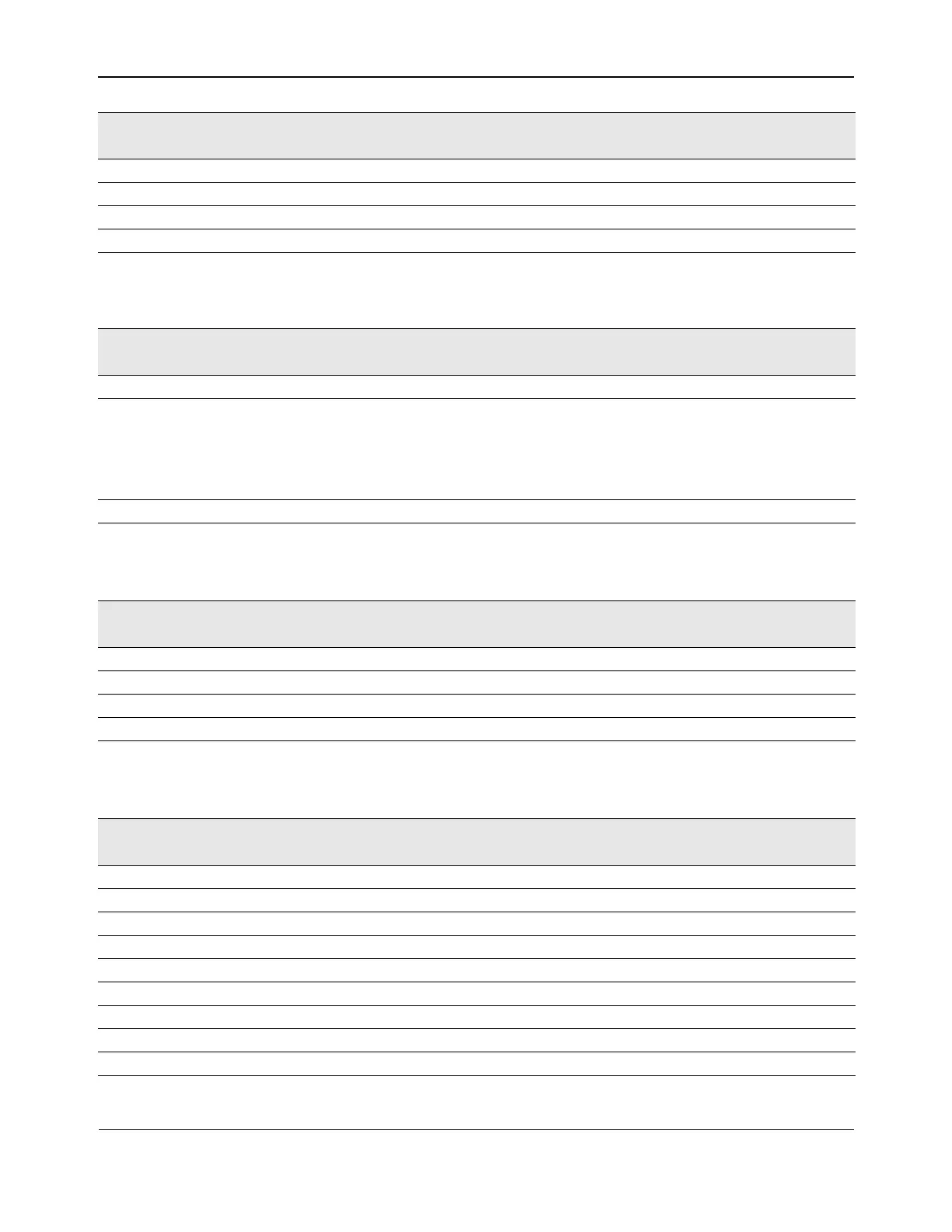

5755ME Miscellaneous Control Register (offset: 0x68B0)

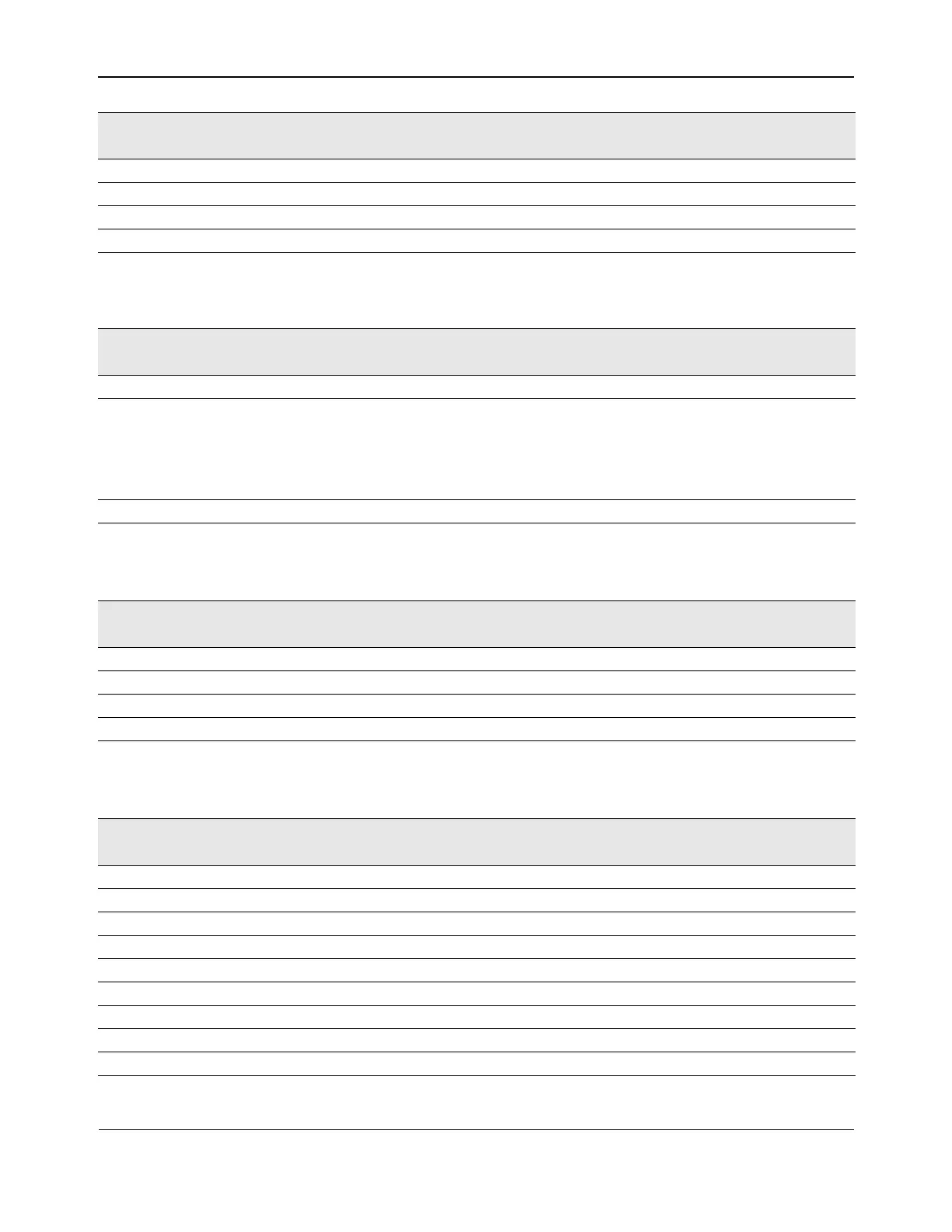

Memory TM control1 (offset: 0x68E0)

Memory TM control 2 (offset: 0x68E4)

ipllpowerdown 3 RO X PLL Power Down Status

Iclkreq_oe_l 2 RO X Clock Request Output Enable

obsvElecIdle 1 RO X Observe Electrical Idle Status

PLLisUp 0 RO X PCIE PLL Status

Name Bits Access

Default

Value

Description

Reserved 31:19 RW X –

EMAC Legacy Bug Fix 18 RW 0 This bit when set enable the EMAC to receive

packet without dropping it after receiving a short

invalid packet size.

1: Enable Bug Fix

0: Disable Bug Fix

Reserved 17:0 RW X –

Name Bits Access

Default

Value

Description

Reserved 31:24 RW 0x0 –

Memory TM control retrybuf 23:16 RW 0x00 TM control of retry buffer

Memory TM control txmbuf 15:8 RW 0x00 TM control for txmbuf

Memory TM control rxmbuf 7:0 RW 0x00 TM control for rxmbuf

Name Bits Access

Default

Value

Description

Reserved 31:29 RW 0x0 –

APE ROM tm 28:24 RW 0x0 TM control for APE ROM (mac0 only).

APE SCPAD2 mem tm 23:20 RW 0x0 TM control for APE SCPAD 0 (mac0 only).

APE SCPAD1 mem tm 19:16 RW 0x0 TM control for APE SCPAD 0 (mac0 only).

APE SCPAD0 mem tm 15:12 RW 0x0 TM control for APE SCPAD 0 (mac0 only).

APE ARB mem tm 11:10 RW 0x0 TM control for APE ARB.

APE ATB mem tm 9:8 RW 0x0 TM control for APE ATB.

APE shared mem tmb 7:4 RW 0x0 TMb control for APE shared mem.

APE shared mem tma 3:0 RW 0x0 TMa control for APE shared mem.

Name Bits Access

Default

Value

Description

Loading...

Loading...