Message Signaled Interrupt RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 467

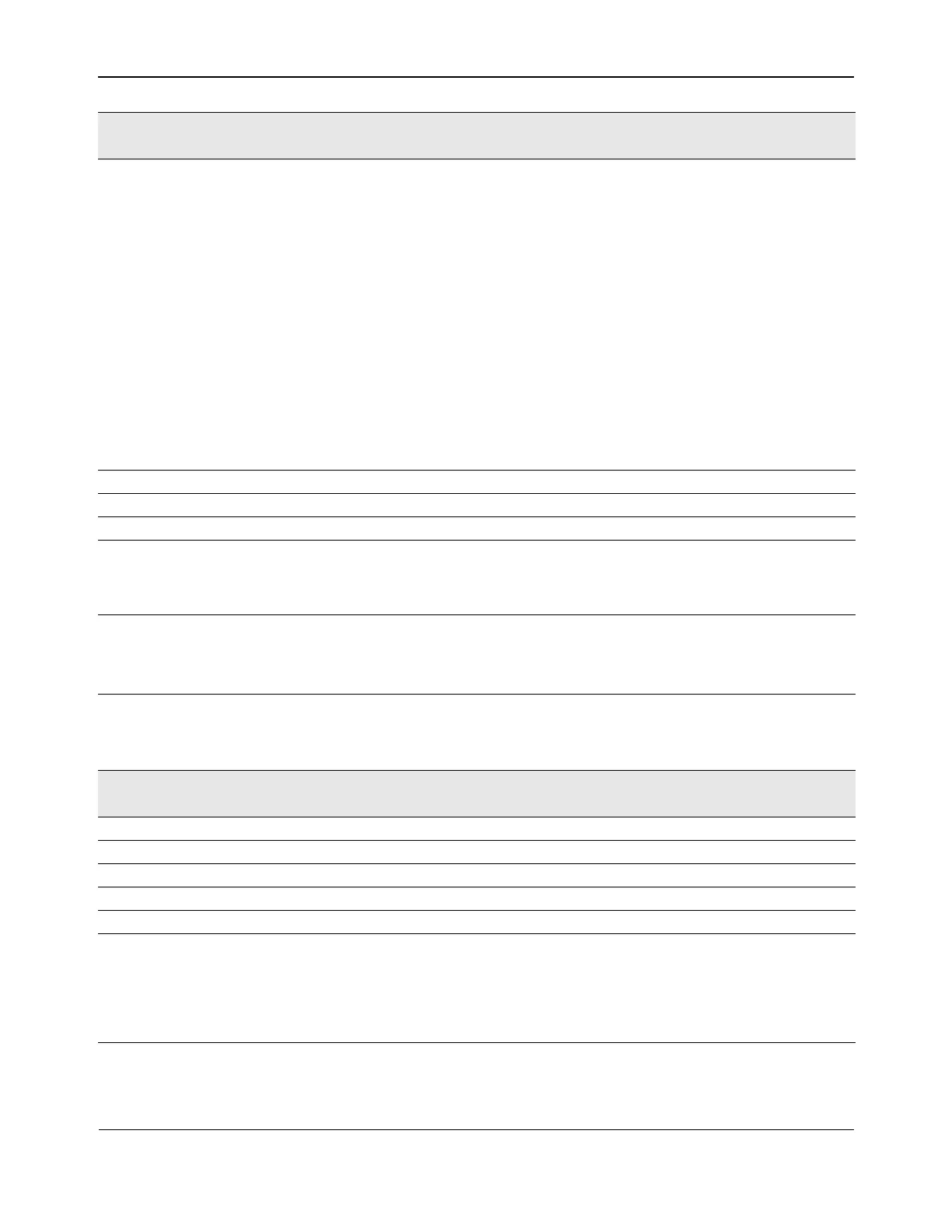

MSI Status Register (offset: 0x6004)

MSI Single Shot Disable 5 RW 0 Disable MSI Single Shot mode.

1: Disable One-Shot MSI mode

0: Enable One-Shot MSI mode

One-Shot MSI mode works in conjunction with

Tag Interrupt mode. The Tag Interrupt mode is

enabled by setting bit 9 of Register 0x68. When

One-Shot MSI mode is enabled, the hardware

automatically auto-mask and auto-acknowledge

when MSI Interrupt is generated by the

hardware. Software needs to un-mask the

interrupt after it has serviced the current MSI

Interrupt to allow future interrupt to generate by

the hardware. The mechanism for software to un-

mask the interrupt is by writing to the mailbox

register bits 31:24 with the same Tag value that

was DMAed to the Host in the last Status Block

update. See note below.

PCI Parity Error Attn 4 RW 0 PCI parity error attention enable.

PCI Master Abort Attn 3 RW 0 PCI master abort attention enable.

PCI Target Abort Attn 2 RW 0 PCI target abort attention enable.

Enable 1 RW 1 This bit controls whether the MSI state machine

is active or not. When set to 0, it completes the

current operation and cleanly halts. Until it is

completely halted, it remains one when read.

Reset 0 RW 0 When this bit is set to 1, the MSI state machine is

reset. This is a self-clearing bit.

Note: If not using Tagged Status mode, the driver

should set 0x6000 bit 5.

Name Bits Access

Default

Value

Description

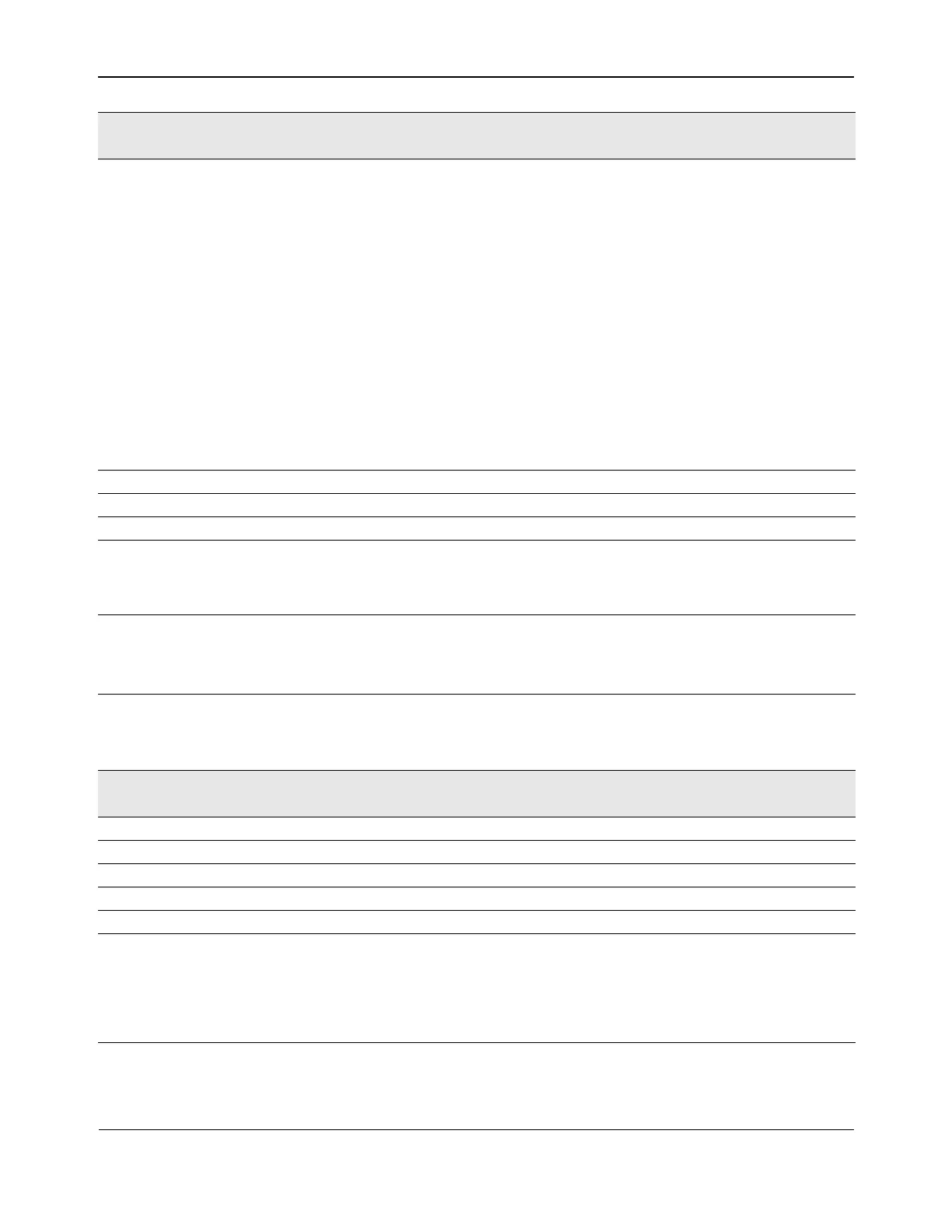

Reserved 31:5 RO 0 –

PCI Parity Error 4 W2C 0 PCI parity error status

PCI Master Abort 3 W2C 0 PCI master abort status

PCI Target Abort 2 W2C 0 PCI target abort status

Reserved 1 RO 0 –

MSI PCI Request 0 RW 0 Reading this bit returns the current status of the

request to PCI to send an MSI. If a value of 1 is

read, then the request is currently asserted.

Writing this bit with a value of one will cause the

request to be asserted. Writing this bit with a

value of 0 has no effect.

Name Bits Access

Default

Value

Description

Loading...

Loading...