PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 294

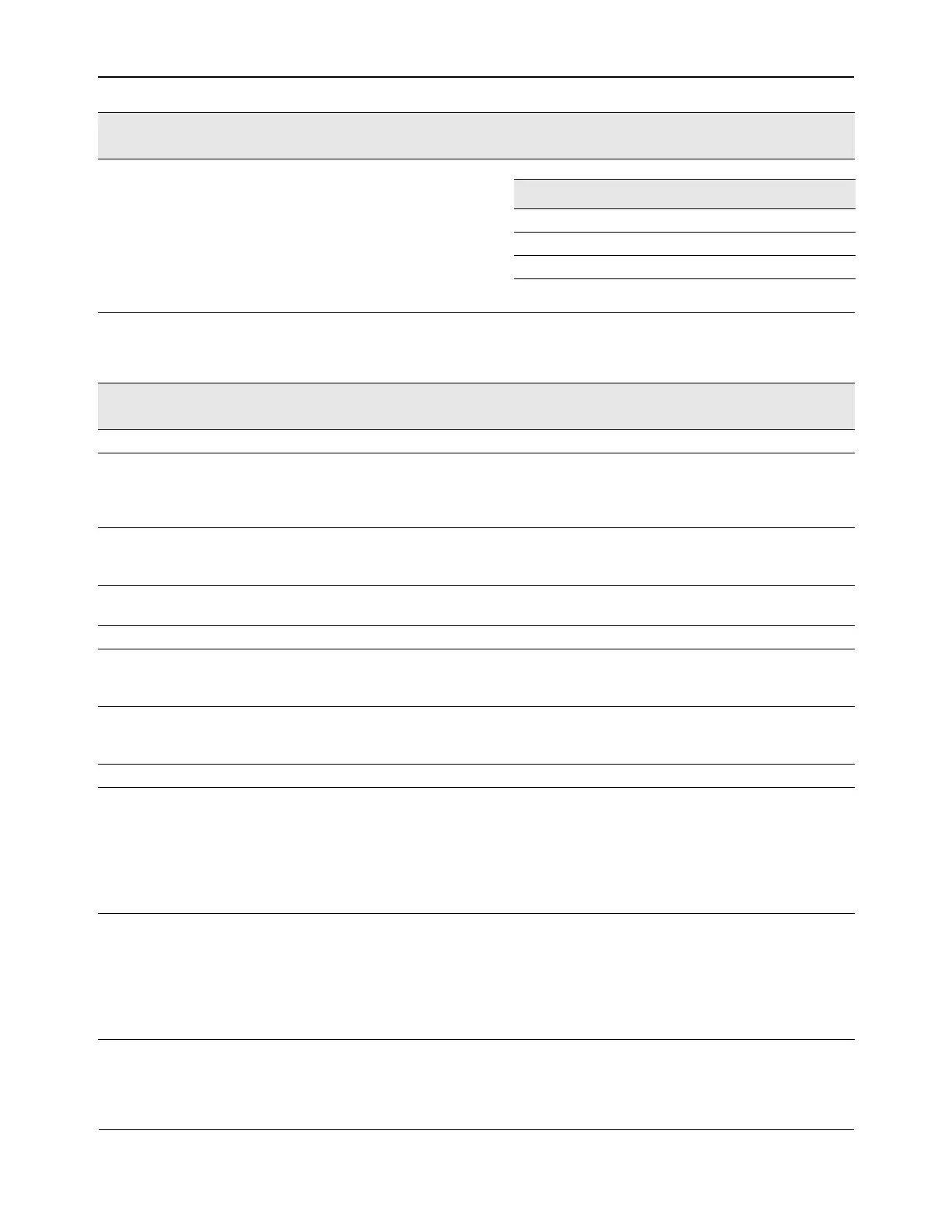

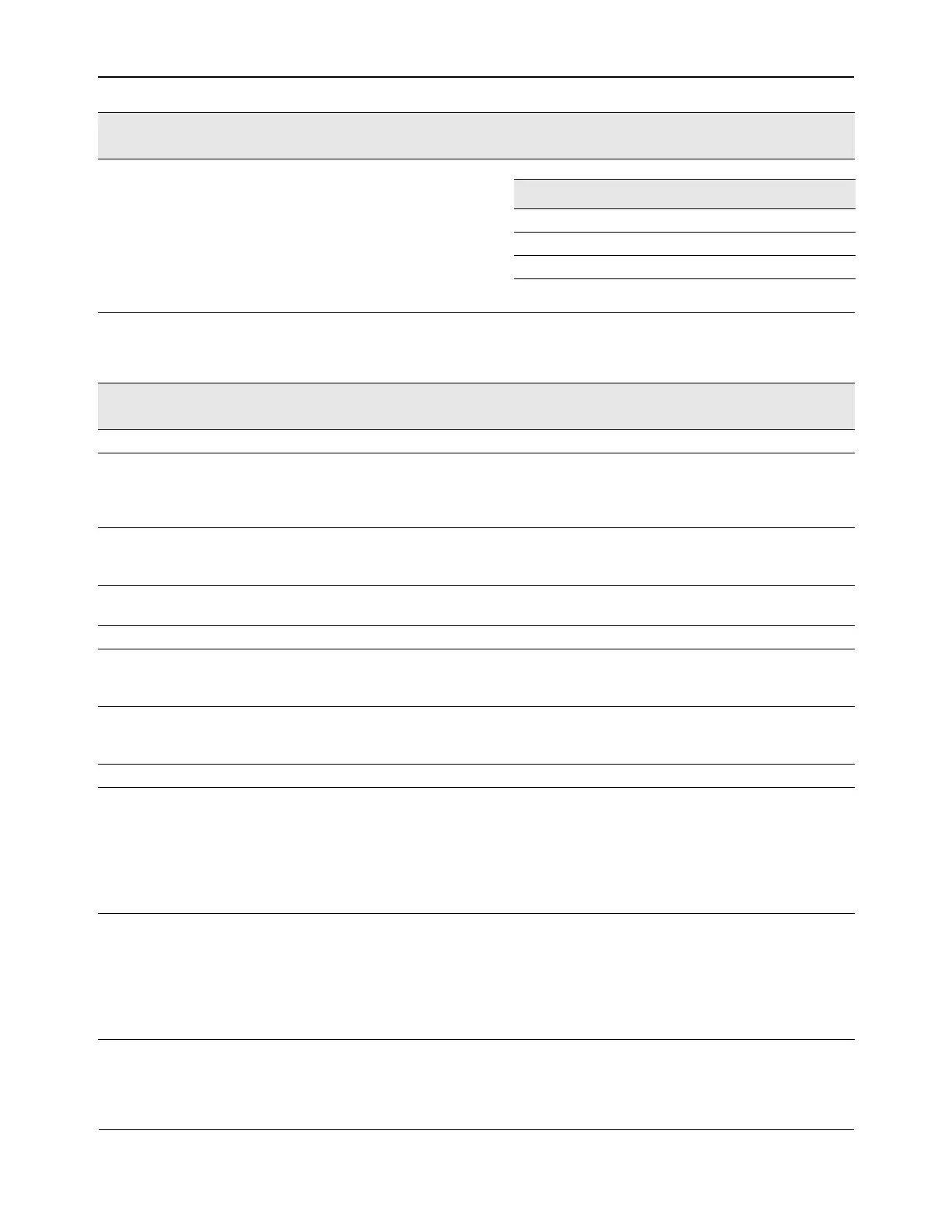

LINK_STATUS_CONTROL – 0xbc

MAX_LINK_SPEED 3:0 RO 0x1

Name Bits Access

Default

Value

Description

Unused3 31:30 RO 0 –

DL_ACTIVE 29 RO 0 Data Link Layer Link Active: returns a 1b to

indicate the DL_Active state, 0b otherwise. Not

implemented and hardwire to 0.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

SLOT_CLK_CONFIG 28 RO 0x1 Slot Clock configuration. This bit is read-only by

host, but read/write via backdoor CS bus.

Path= i_cfg_func.i_cfg_private

LINK_TRAINING 27 RO 0 EP: This bit is N/A and is hardwired to 0.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

Unused2 26 RO 0 –

NEG_LINK_WIDTH 25:20 RO 0 Negotiated Link Width. These bits indicate the

negotiated link width of the PCI Express link.

Path= i_pl_top.i_pl_ltssm

NEG_LINK_SPEED 19:16 RO 0 Link Speed. These bits indicate the negotiated link

speed of the PCI Express link.

Path= i_pl_top.i_pl_ltssm

Unused1 15:12 RO 0 –

LINK_BW_INT_EN 11 RO 0 Link Autonomous Bandwidth Interrupt Enable:

When Set, this bit enables the generation of an

interrupt to indicate that the Link Autonomous

Bandwidth Status bit has been Set. RC: Not

implemented and hardwired to 0. EP: N/A and

hardwired to 0

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

LINK_BW_MGMT_INT_EN 10 RO 0 Link Bandwidth Management Interrupt Enable:

when Set, this bit enables the generation of an

interrupt to indicate that the Link Bandwidth

Management Status bit has been Set. RC: N/A

and hardwired to 0. EP: Not implemented and

hardwired to 0.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

Name Bits Access

Default

Value

Description

Value Name Description

0 64 64 Bytes

1 128 128 Bytes

255 – end_of_table

Loading...

Loading...