PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 293

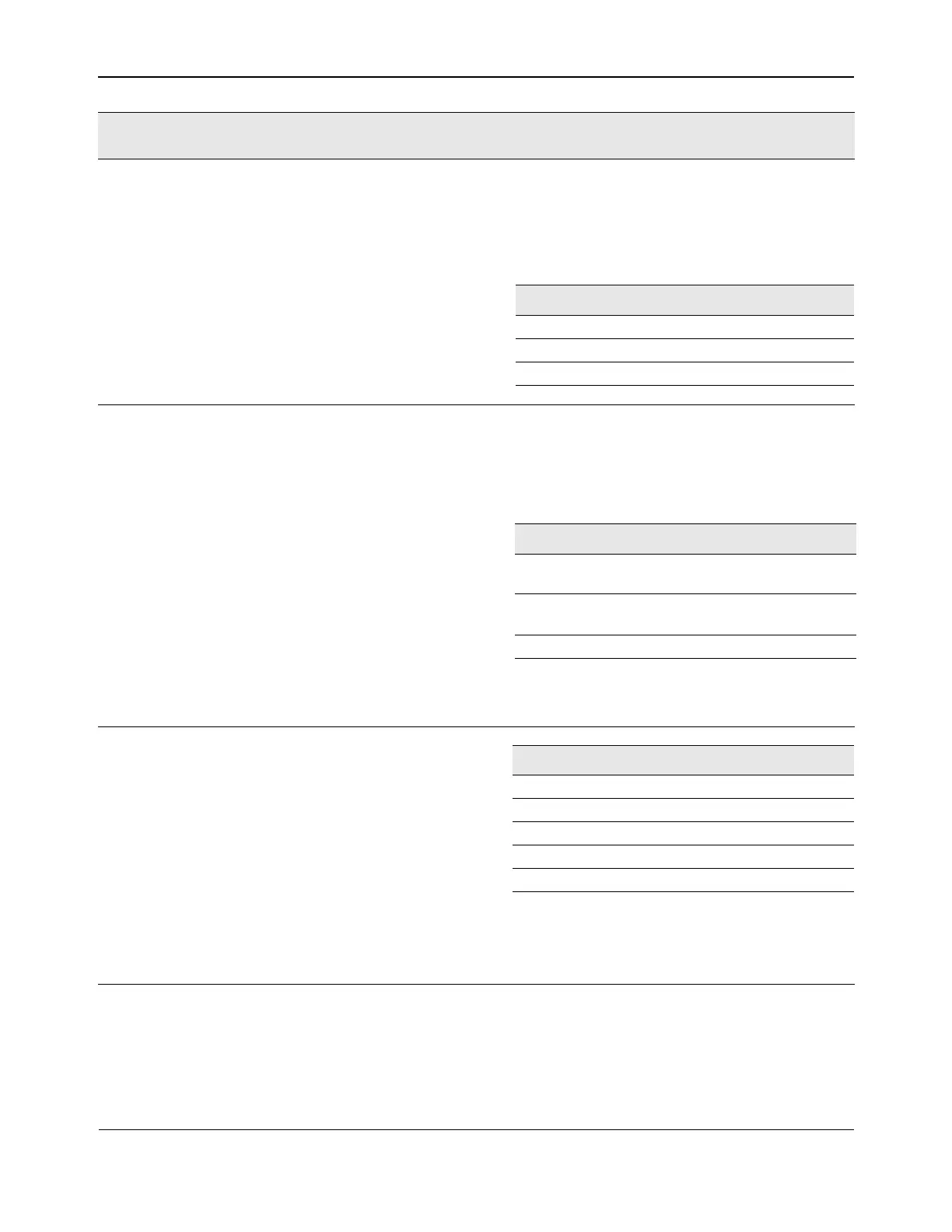

L1_EXIT_LAT 17:15 RO 0x2 L1 Exit Latency. These bits are programmable

through register space.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

Depending on whether device is in common clock

mode or not, the value reflected by these bits is

one of the following.

L0S_EXIT_LAT 14:12 RO 0x5 L0s Exit Latency. These bits are programmable

through register space.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

Depending on whether device is in common clock

mode or not, the value reflected by these bits is

one of the following.

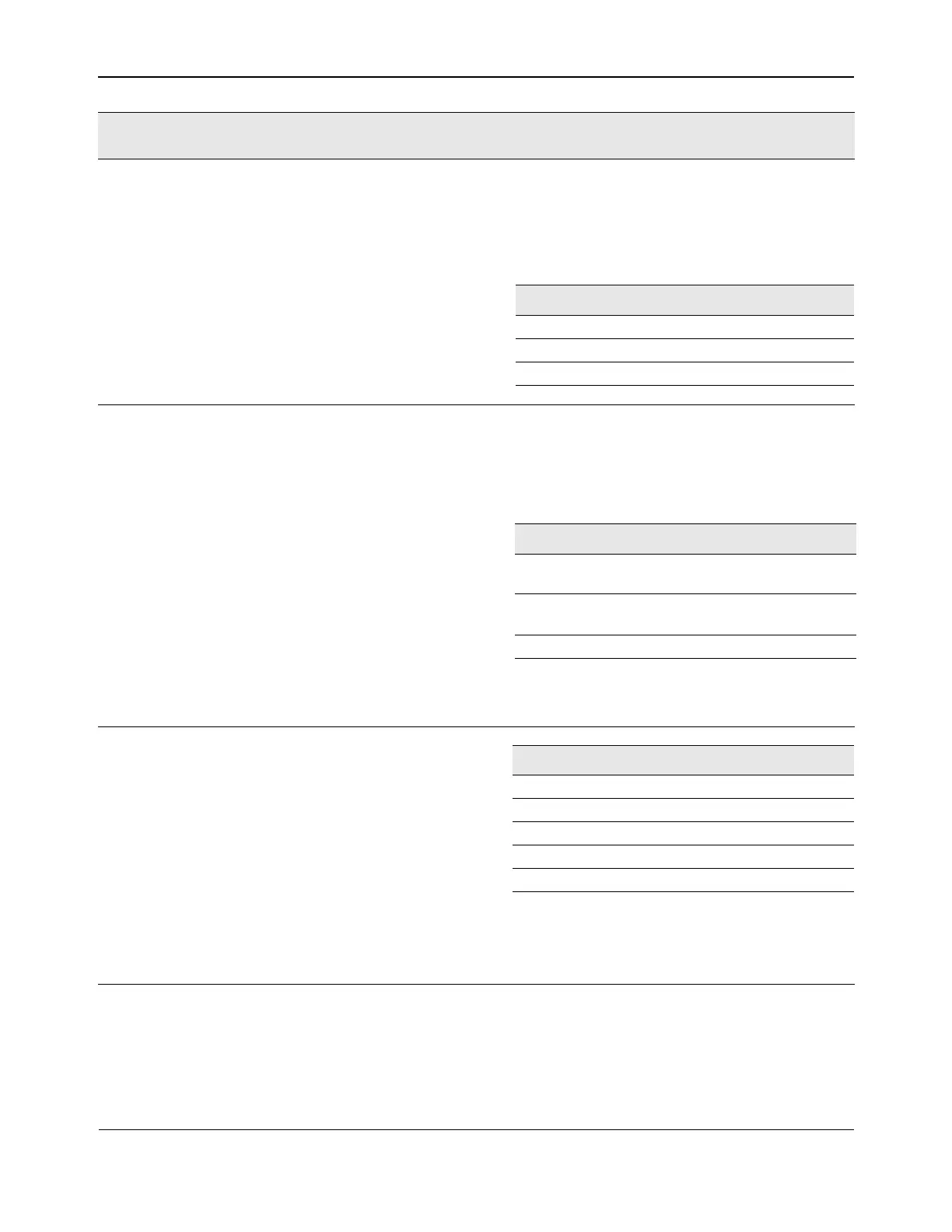

ASPM Support. These bits are programmable

through reg space.

Path= i_cfg_func.i_cfg_private

ASPM_SUPT 11:10 RO 0x3

Path= i_cfg_func.i_cfg_private Value used by

internal logic is the smaller of the value

programmed for each function

Name Bits Access

Default

Value

Description

Value Name Description

1 1_2 L1 exit latency of 1 us to 2 us.

2 2_4 L1 exit latency of 2 us to 4 us.

255 – end_of_table

Value Name Description

4 0_1 L0s exit latency of 512

ns to 1 us.

5 1_2 L0s exit latency of 1 us

to 2 us.

255 – end_of_table

Value Name Description

0RES_0Reserved

1 L0S L0s entry supported

2RES_2Reserved

3 L0S_L1 L0s and L1 supported

255 – end_of_table

Loading...

Loading...