Central Power Management Unit (CPMU) RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 399

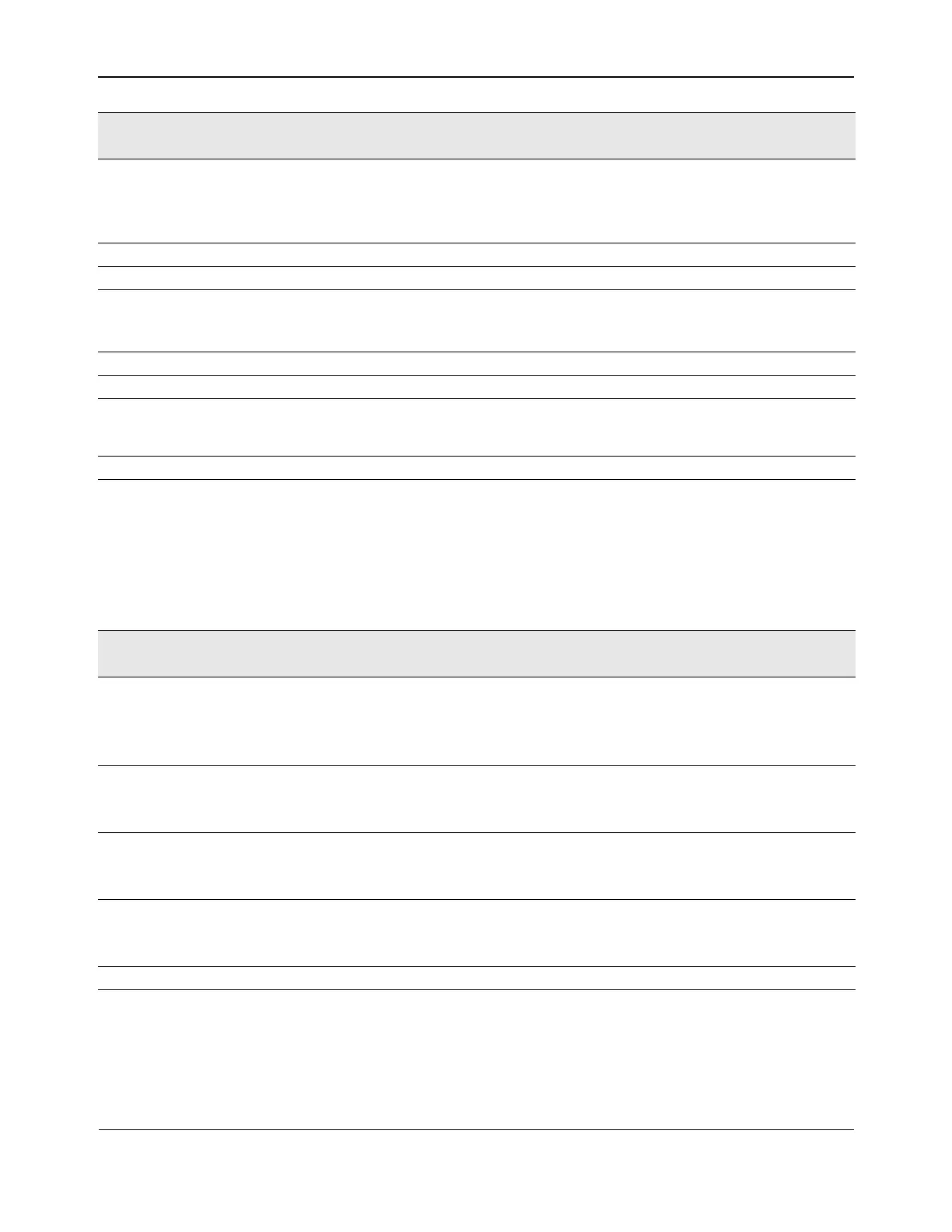

Flash Clock Policy Register (offset: 0x366C)

For BCM5719/5720 only. This register is reset by POR Reset or CPMU Register Software Reset. The Force

Disable bit has higher priority than Override Enable. This register is shared by all 4 MAC ports. User must first

gain grant from the global MUTEX registers (0x36F0 & 0x36F4) before writing to this register.

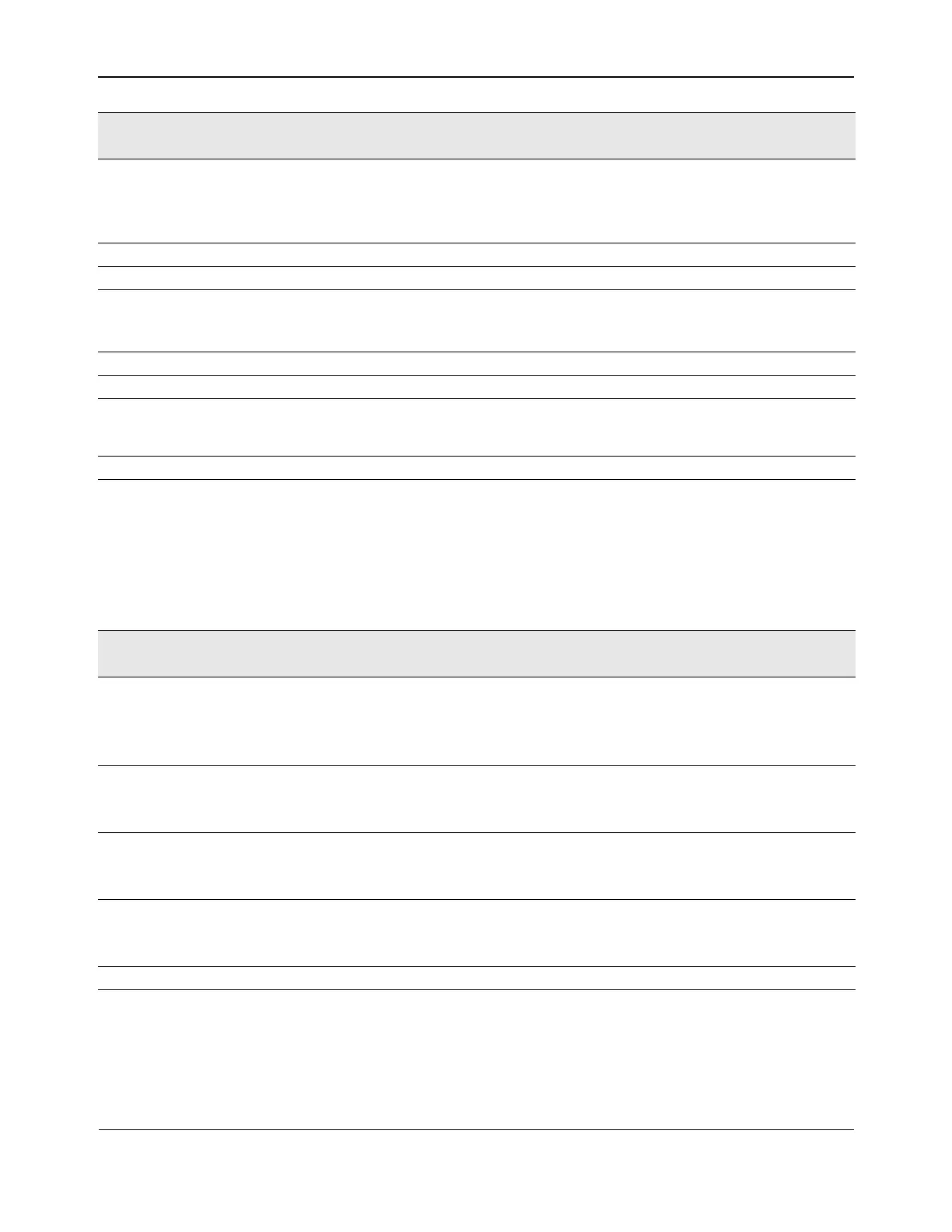

Incorrect checksum on LSO

packets Fix Disable

20 RW 0x0 Disable fix for incorrect checksum on LSO

packets.

1 = Disable

0 = Enable

PCIE pcie_tmux_sel[1:0] 19:18 RW 0x0 –

Reserved 17:13 DC 0 –

PLLisUp signal drive 12 RW 0x0 When 0, force the PLLisUp signal to be 1.

When 1, let the hardware drive the PLLisUp

signal.

PCIE pcie_tmux_sel[3:2] 11:10 RW 0x0 –

Reserved 9 RW 0 –

Capability version for

completion timeout ECN for

PCIE 1.1

8 RW 0x0 1 = Version 1; Fix Disable

0 = Version 2; Fix Enable

Reserved 7:0 DC 0x0 –

Name Bits Access

Default

Value

Description

Flash Clock Speed 31 RW 0x0 Enable Flash clock override*.

Override Enable

1: Enable Flash clock override

0: Disable Flash clock override

Force Flash Clock Disable 30 RW 0x0 Flash clock Disable*.

1: Disable Flash clock

0: Enable Flash clock

Flash Idle mode Enable 29 RW 0x0 Flash Idle mode Enable

1: Enable Flash Idle mode

0: Disable Flash Idle mode

Force EAV Clock Disable 28 RW 0x0 EAV clock Disable

1: Disable EAV clock

0: Enable EAV clock

Reserved 27:20 DC 0 –

Name Bits Access

Default

Value

Description

Loading...

Loading...