Endian Control (Byte and Word Swapping)BCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 196

The only side effect for a little endian host that sets the Enable Endian Word Swap bit would be that the driver

would have to perform an additional word swap on any 64-bit fields (e.g., a 64-bit physical address) that were

given to the driver by the Network Operating System (NOS).

Little-endian hosts will not want to set the Enable Endian Byte Swap bit for target accesses. This bit is intended

to be used by big endian systems that needed PCI data (little endian) translated back to big endian format.

The following figures show the translation of data when the Enable Endian Byte Swap bit is set:

Internal Byte Ordering PCI Byte Ordering

0x04 8C 8D 8E 8F 8C 8D 8E 8F 0x04

Note: Some big endian systems automatically do this depending on the architecture of the host’s PCI

to memory interface.

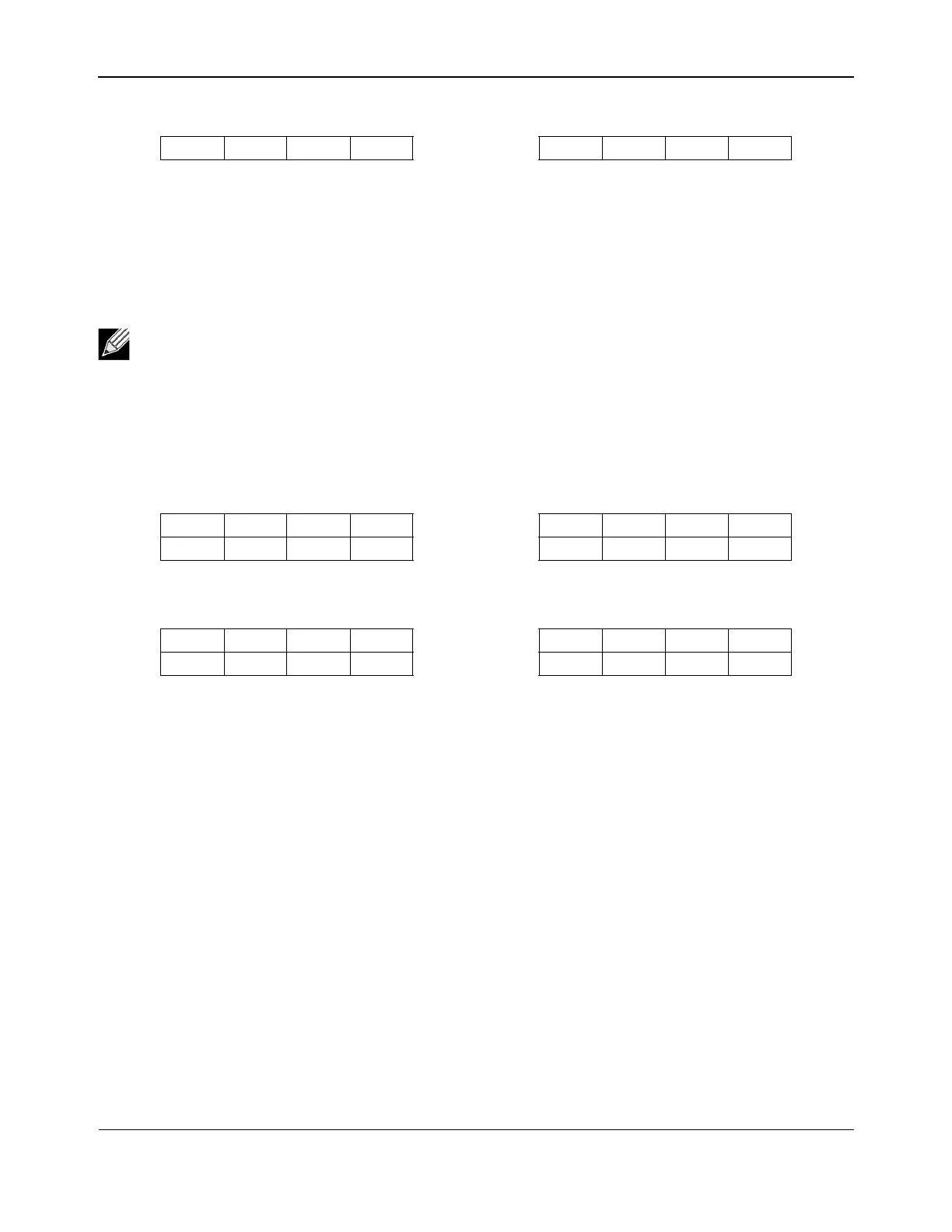

Table 58: Byte Swap Enable Translation on 32-Bit PCI (No Word Swap)

Internal Byte Ordering PCI Byte Ordering

31 16 15 0 31 16 15 0

0x00 88 89 8A 8B 8F 8E 8D 8C 0x00

0x04 8C 8D 8E 8F 8B 8A 89 88 0x04

31 16 15 0 31 16 15 0

0x00 88 89 8A 8B 8B 8A 89 88 0x00

0x04 8C 8D 8E 8F 8F 8E 8D 8C 0x04

Table 57: Internal Byte OrderingPCI Byte Ordering (Cont.)

Loading...

Loading...