PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 288

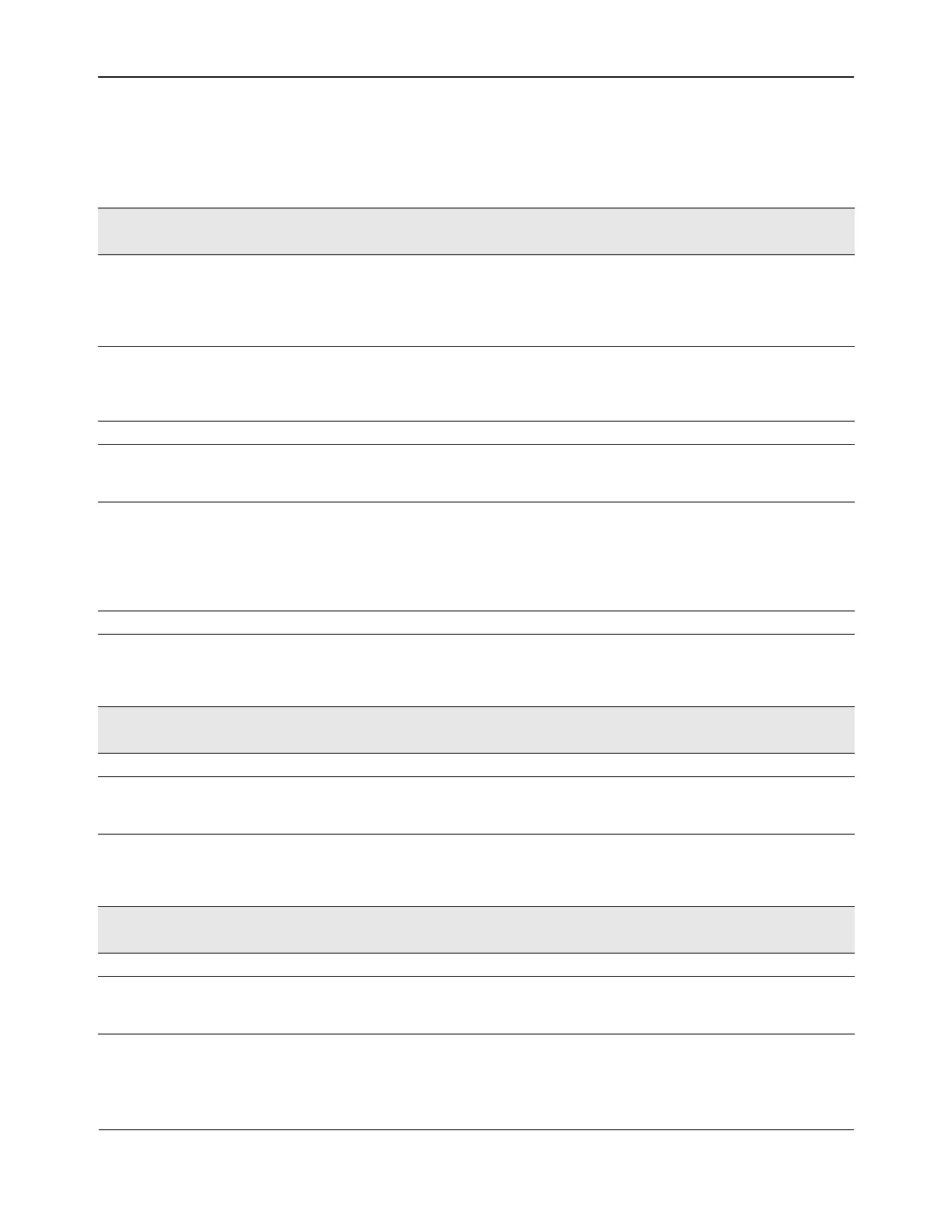

MSI-X Capabilities Registers

MSI-X Capability Header Register (offset: 0xA0)

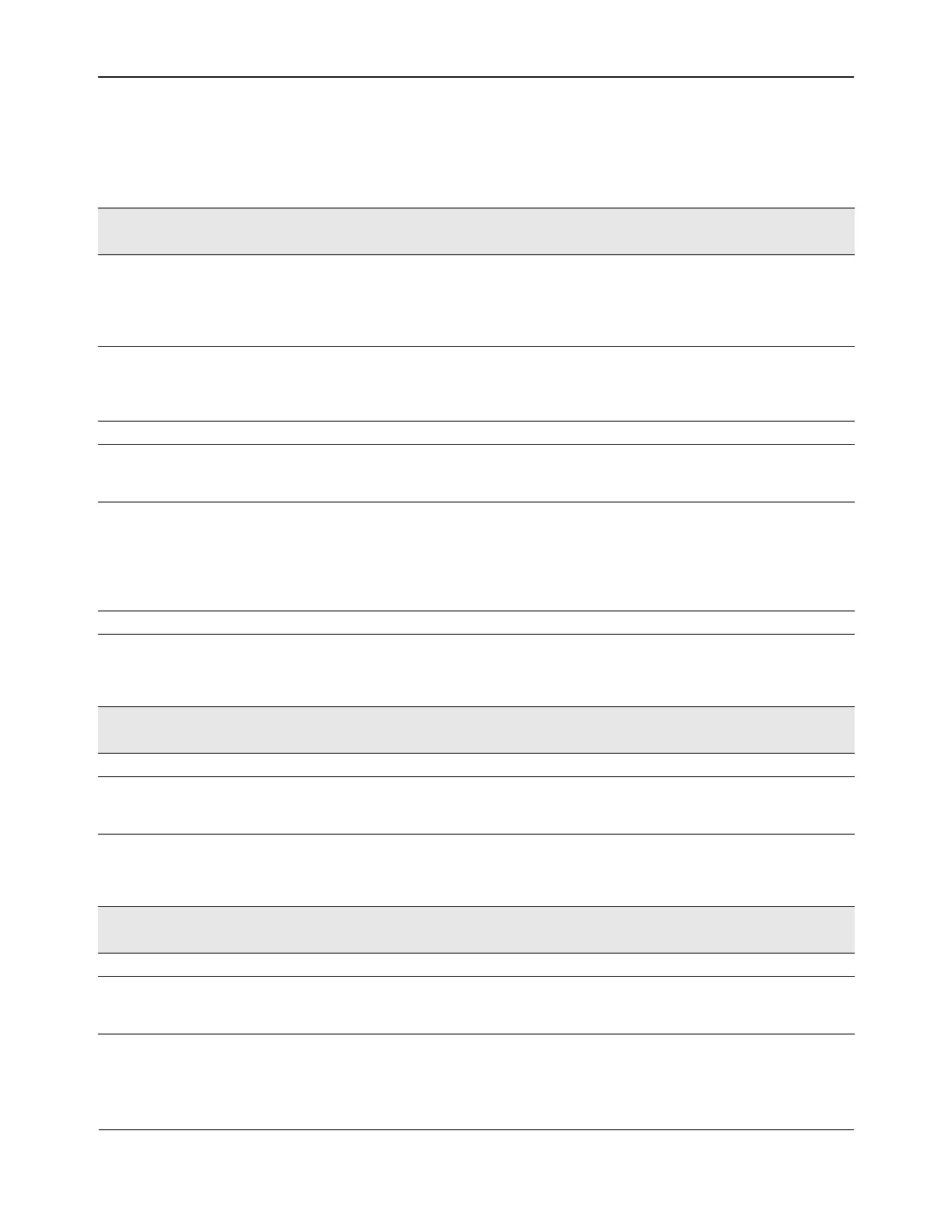

MSIX_TBL_OFF_BIR – 0xa4

MSIX_PBA_BIR_OFF – 0xa8

Name Bits Access

Default

Value

Description

MSIX_ENABLE 31 RW 0 If 1 and the MSI enable bit in the MSI message

control register is 0, the function is permitted to

use MSIX request service and profited from using

INTx# messages.

Path = i_cfg_func.i_cfg_public.i_cfg_msi_cap

FUNC_MASK 30 RW 0 If 1, all of the vectors associated with the function

are masked regardless of their per vector Mask

bit.

Path = i_cfg_func.i_cfg_public.i_cfg_msi_cap

RESERVED 29:27 RO 0 Reserved

TABLE_SIZE 26:16 RO 0 System sw reads this field to determine the MSI-X

table size N, which is encoded as N-1

Path = i_cfg_func.i_cfg_private

MSIX_NEXT_CAP_PTR 15:8 RO 0xac This value continues the PCI capability chain. It's

value specified as offset in the PCI address space

of the next capability. The read-only value of this

register is controlled by the CAP_ENA register in

the PCI register space.

Path = i_cfg_func.i_cfg_public.i_cfg_ep_reg

MSIX_CAP_ID 7:0 RO 0x11 Capability ID for MSIX Path = cfg_defs

Name Bits Access

Default

Value

Description

TABLE_OFFSET 31:3 RO 0 Path = i_cfg_func.i_cfg_private

TABLE_BIR 2:0 RO 0 Indicates which one of functions BAR is used to

map MSI-X table into memory space.

Path = i_cfg_func.i_cfg_private

Name Bits Access

Default

Value

Description

TABLE_OFFSET 31:3 RO 0 Path = i_cfg_func.i_cfg_private

TABLE_BIR 2:0 RO 0 Indicates which one of functions BAR is used to

map MSI-X table into memory space.

Path = i_cfg_func.i_cfg_private

Loading...

Loading...