Central Power Management Unit (CPMU) RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 409

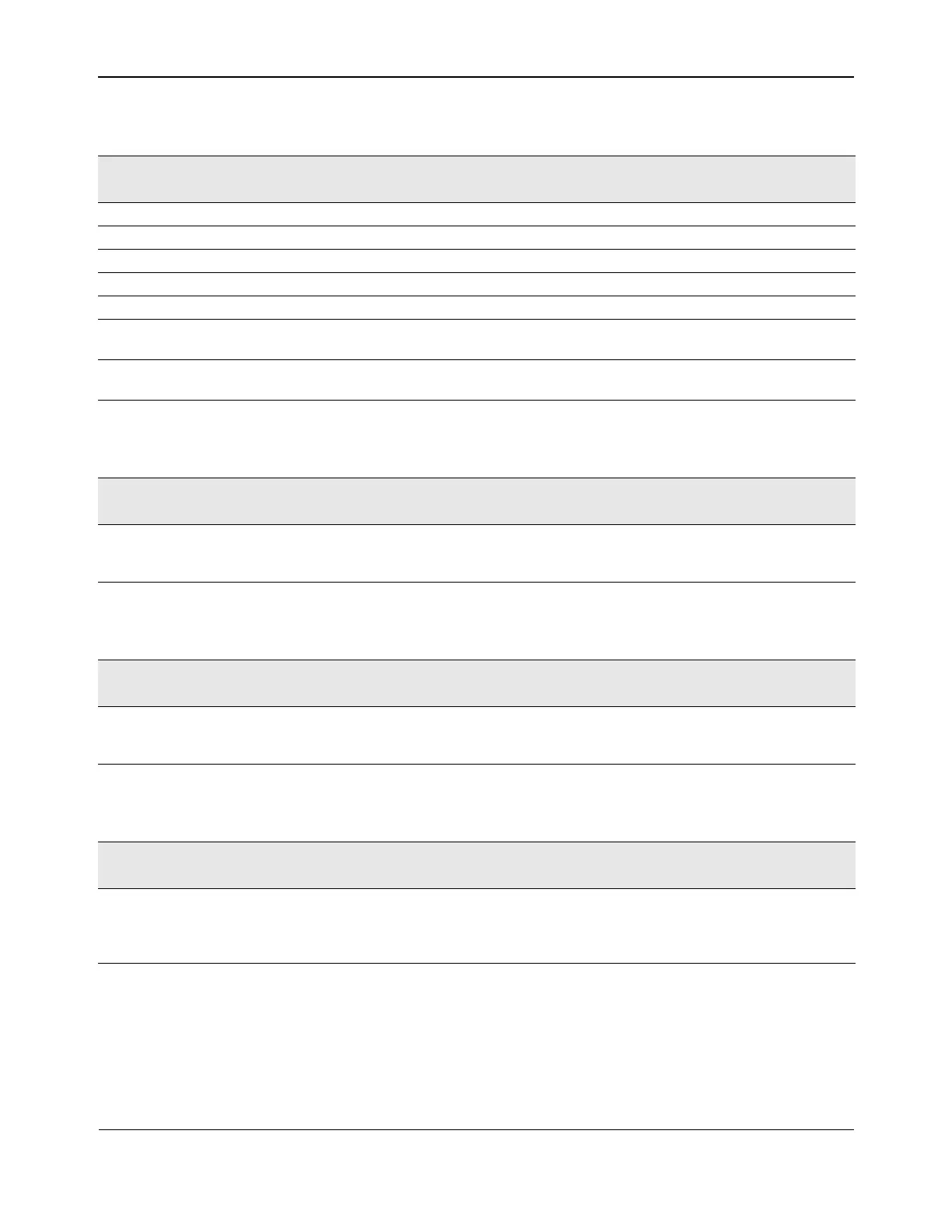

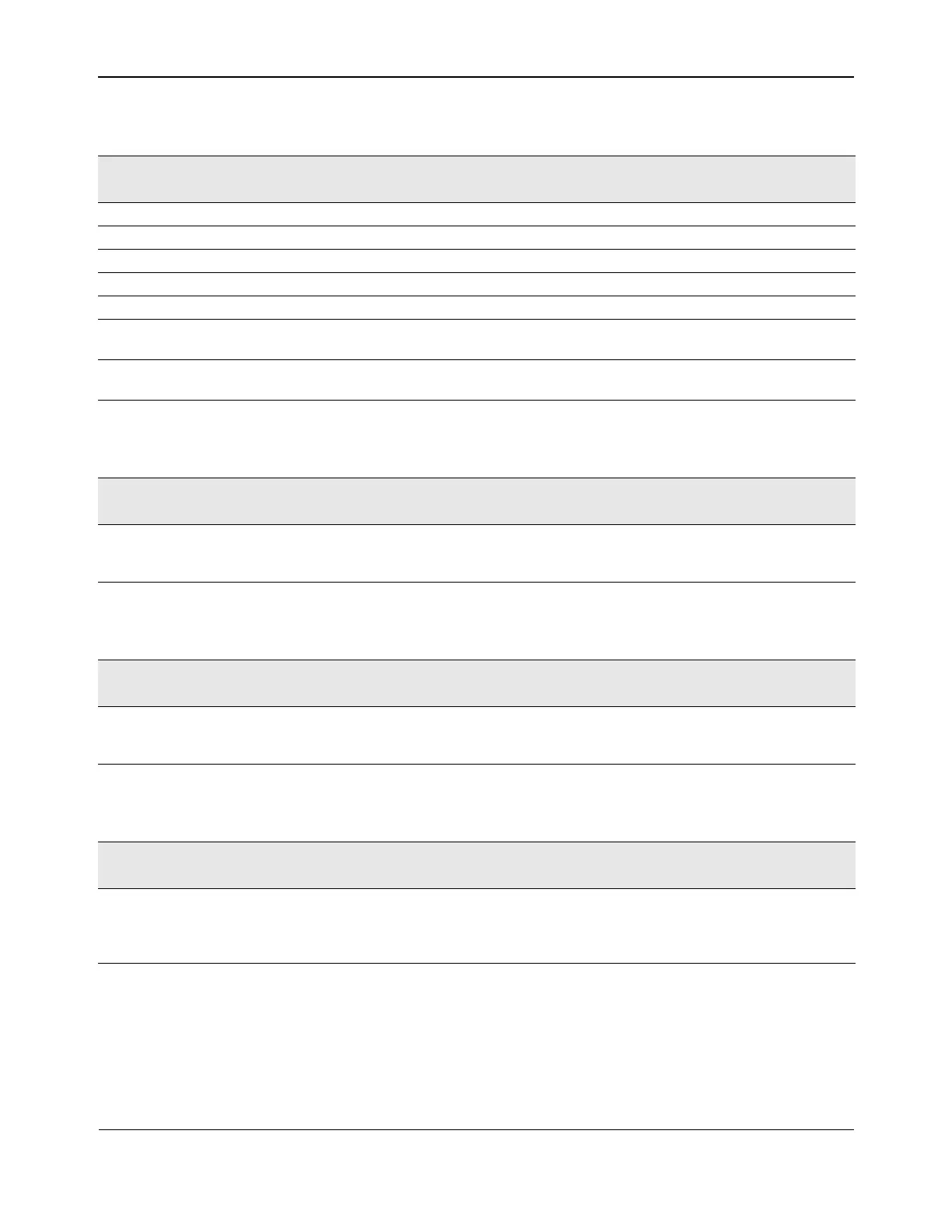

EEE Link Idle Status Register (offset: 0x36C0)

EEE Statistic Counter 1 Register (offset: 0x36C4)

EEE Statistic Counter 2 Register (offset: 0x36C8)

EEE Statistics Counter 3 Register (offset: 0x36CC)

Name Bits Access

Default

Value

Description

Reserved 31:25 RO 0x0 –

PCIE not in L0 State 24 RO 0x0 PCIE is in L0s, L1 or L2 state.

Reserved 23:4 RO 0x0 –

MDIO Idle 3 RO 0x0 No on-going MDIO access.

Debug UART Idle 2 RO 0x0 Debug UART is idle.

APE TX Packet Buffer Empty 1 RO 0x0 Internal packet buffers in APE subsystem for TX

is empty.

LAN TX Packet Buffer Empty 0 RO 0x0 Internal packet buffers in LAN core for TX is

empty.

Name Bits Access

Default

Value

Description

EEE Mode Entering Counter 31:0 RW 0x0 This counter counts the number of times CPMU

goes into EEE mode. The entire 32 bit register

can be cleared by writing 0xFFFFFFFF.

Name Bits Access

Default

Value

Description

Receive LPI Entering Counter 31:0 RW 0x0 This counter counts the number of times the

receive side goes into LPI. The entire 32 bit

register can be cleared by writing 0xFFFFFFFF.

Name Bits Access

Default

Value

Description

EEE Link Idle Entering Counter 31:0 RW 0x0 This counter counts the number of timers the

debounced version of EEE link idle is asserted.

The entire 32 bit register can be cleared by

writing 0xFFFFFFFF.

Loading...

Loading...