SerDes PHY Register DefinitionsBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 556

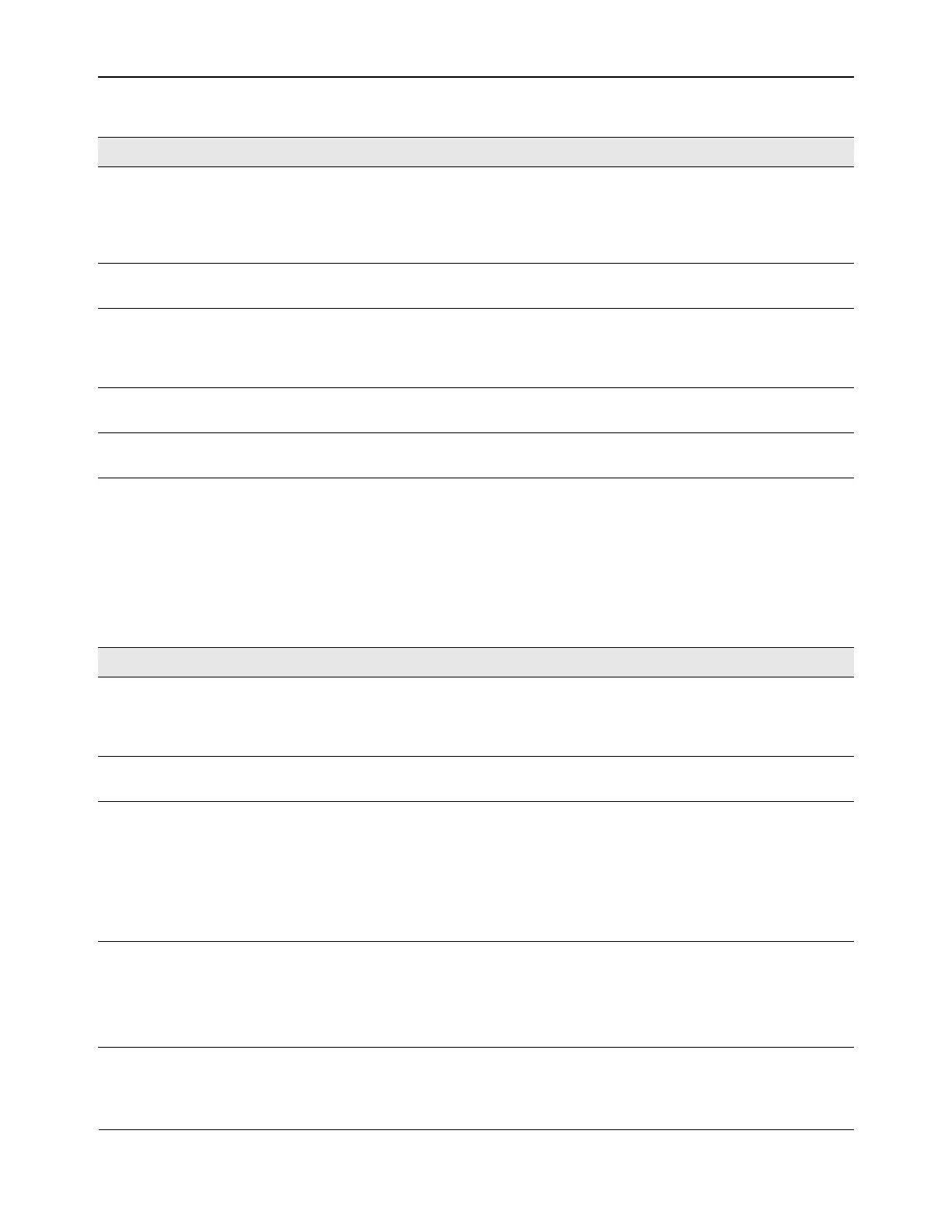

1000XCONTROL2

Register Description: 1000X Control2 Register.

Register Offset: 0x11 at Block 0

4 AUTODET_EN RW 0 = Disable auto detection (fiber or SGMII mode is set

according to bit 0 of this register.)

1 = Enable auto-detection (fiber and SGMII mode will

switch each time a auto-negotiation page is received with

the wrong selector field in bit 0.)

0

3 INVERT_SIG_DET RW 0 = Use signal detect from pin.

1 = Invert signal detect from pin.

1

2 SIGNAL_DETECT_EN RW 0 = Ignore signal detect from pin.

1 = Signal detect from pin must be set in order to achieve

synchronization. In SGMII, the signal detect is always

ignored regardless of the setting of this bit.

1

1 TBI_INTERFACE RW 0 = GMII interface

1 = Ten bit interface.

1

0 FIBER_MODE_1000X RW 0 = SGMII mode

1 = Fiber mode (1000X)

1

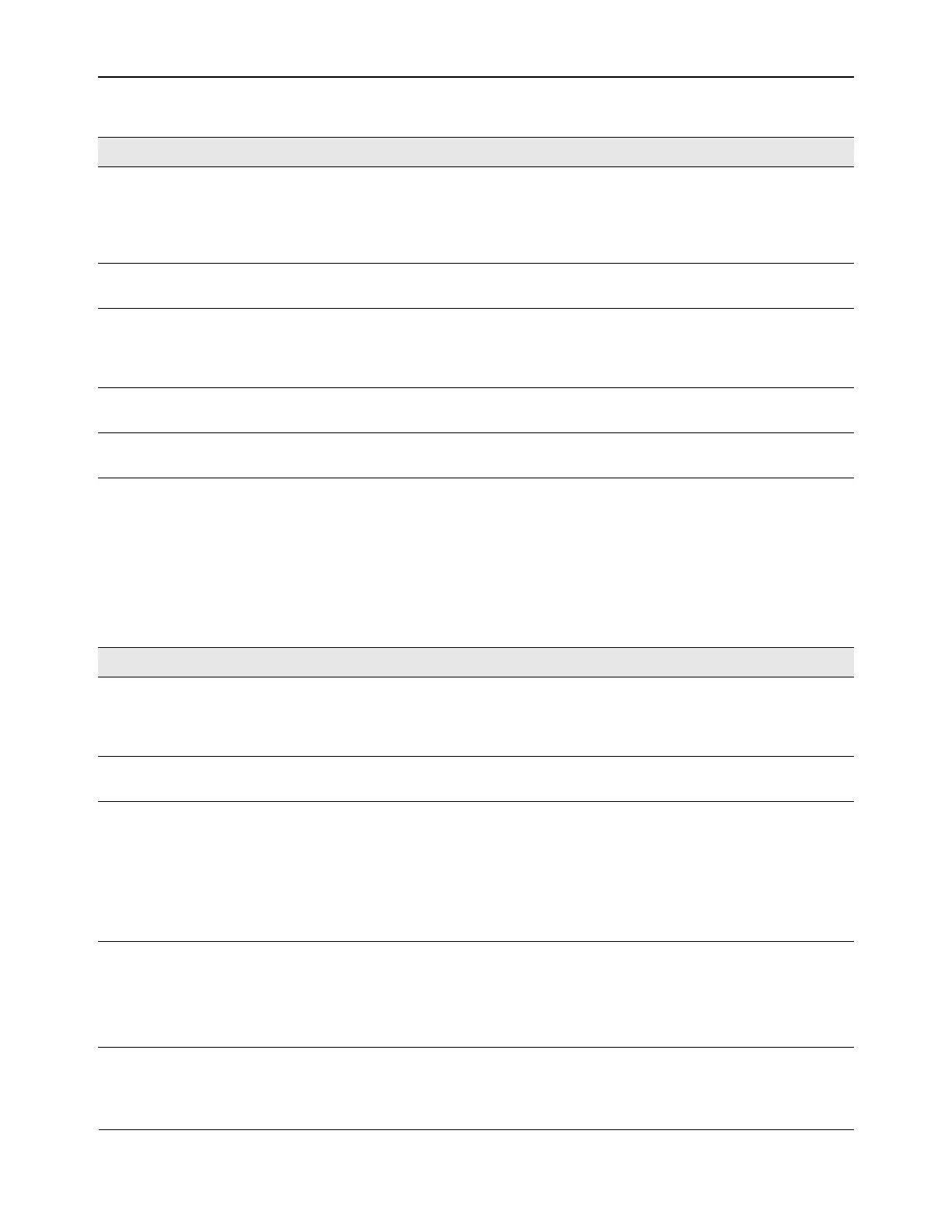

Table 135: 1000XCONTROL2

Bits Name RW Description Default

15 DIS_EXTEND_FDX RW 0 = Normal operation

1 = In full duplex mode, disable carrier extension in pcs

receive when bit[7] of this register is set and disable TRRR

generation in pcs transmit when bit[8] of this register is set.

0

14 CLR_BER_CNTR RW 0 = Normal operation

1 = Clear bit-error-rate counter (register 0*17h bits[15:8])

0

13 TX_IDLE_JAM_SEQ_T

EST

RW Register 0*1dh bits[9:0] will override k28.5 for stage 5

(17Ch).

Register 0*1eh bits[9:0] will override D16.2 for stage 6

(289h).

0 = Normal operation.

1 = Enable 16-stage 10-bit idle transmit test sequence to

SerDes transmitter.

0

12 TX_PKT_SEQ_TEST RW Stage 1-4, 13-16 = idle.

Stage 5-12 = data packet.

0 = Normal operation.

1 = Enable 16-stage 10-bit idle transmit test sequence to

SerDes transmitter.

0

Table 134: 1000XCONTROL1 (Cont.)

Bits Name RW Description Default

Loading...

Loading...