PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 277

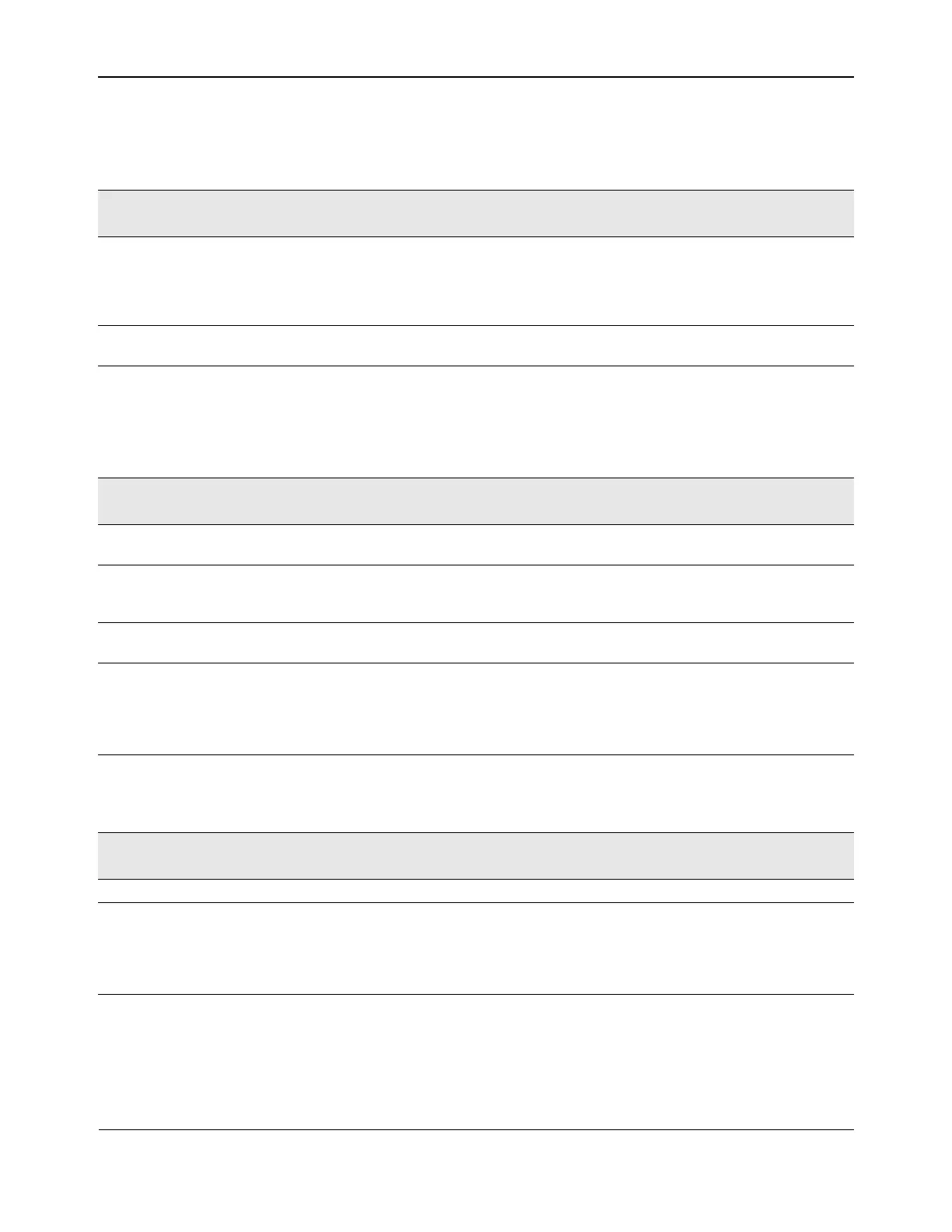

Subsystem ID/Vendor ID Register (offset: 0x2C)

This register is reset by Hard Reset.

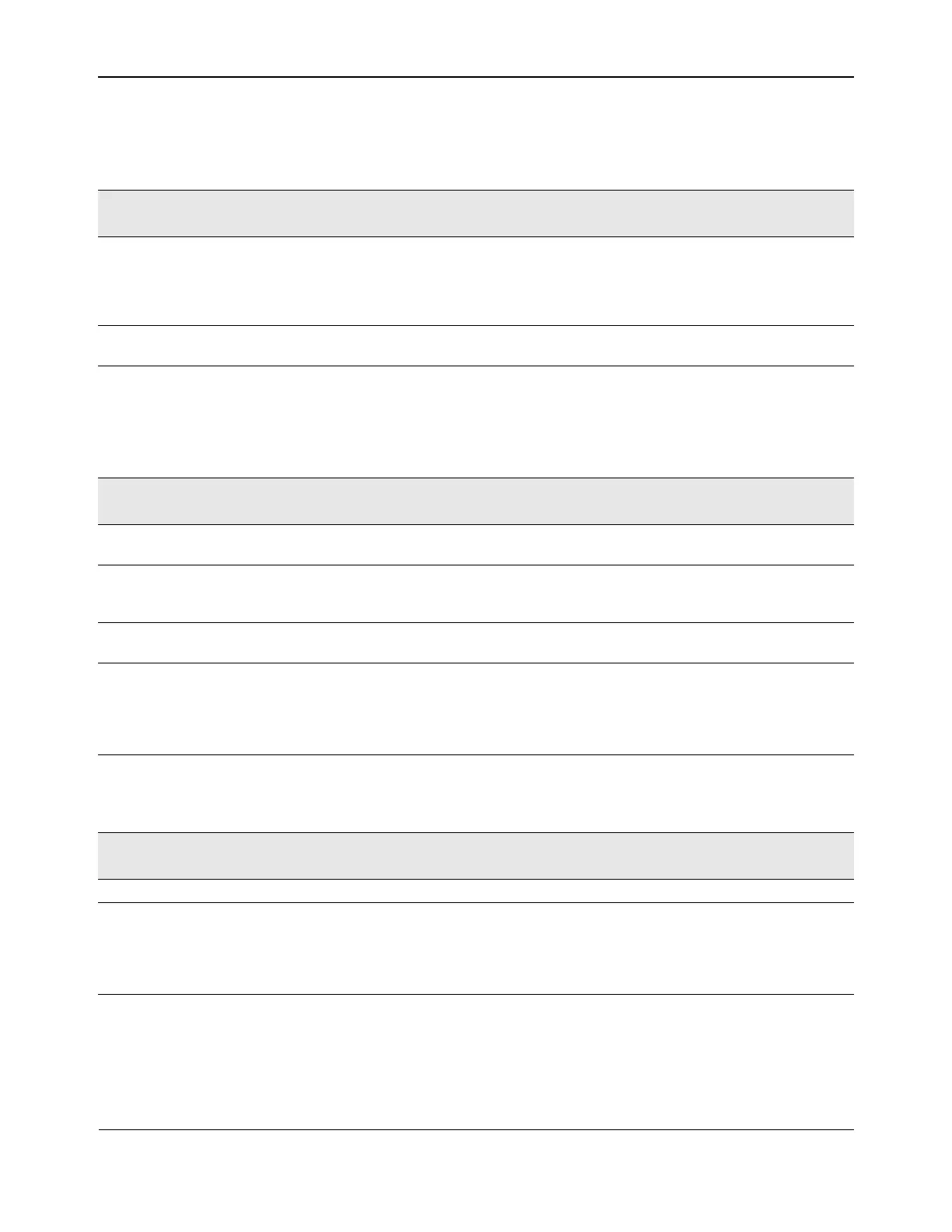

Expansion ROM Base Address Register (offset: 0x30)

This register is reset by PCIE Reset. It becomes aN RW register if bit 5 of PCI State Register is set.

Capabilities Pointer Register (offset: 0x34)

Name Bits Access

Default

Value

Description

Subsystem

Device ID

31:16 RO – Default for BCM5717 (LAN Function 0): 0x1655

Default for BCM5719 (LAN Function 0): 0x1657

Default for BCM5718 (LAN Function 0): 0x1656

Default for BCM5720 (LAN Function 0): 0x165F

Subsystem

Vendor ID

15:0 RO 0x14E4 Identifies board manufacturer

Name Bits Access

Default

Value

Description

ROM Base

Address

31:24 RW 0xXXXX These bits indicate the address of the Expansion ROM

area.

ROM Size

indication

23:11 RW 0x00 These bits indicate the size of the Expansion ROM area

or the address of it. The boundary form RO bits to RW

bits is controlled by the EXP_ROM_SIZE bits.

Reserved 10:1 RO 0x000 These bits indicate that the Expansion ROM area is at

least 2k bytes. They always read as zero. P

Expansion ROM

Enable

0 RW 0x0 This bit indicates that the Expansion ROM BAR is valid

when set to one. If it is zero, the expansion BAR should

not be programmed or used. This bit will only be RW if

it is enabled by the EXP_ROM_ENA bit which defaults

to 0.

Name Bits Access

Default

Value

Description

Reserved 31:8 RO 0x0 Unused

Capabilities

pointer

7:0 RO 0x48 The 8-bit Capabilities Pointer register specifies an

offset in the PCI address space of a linked list of new

capabilities. The capabilities are PCI-X, PCI Power

Management, Vital Product Data (VPD), and Message

Signaled Interrupts (MSI) is supported.

Loading...

Loading...