PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 301

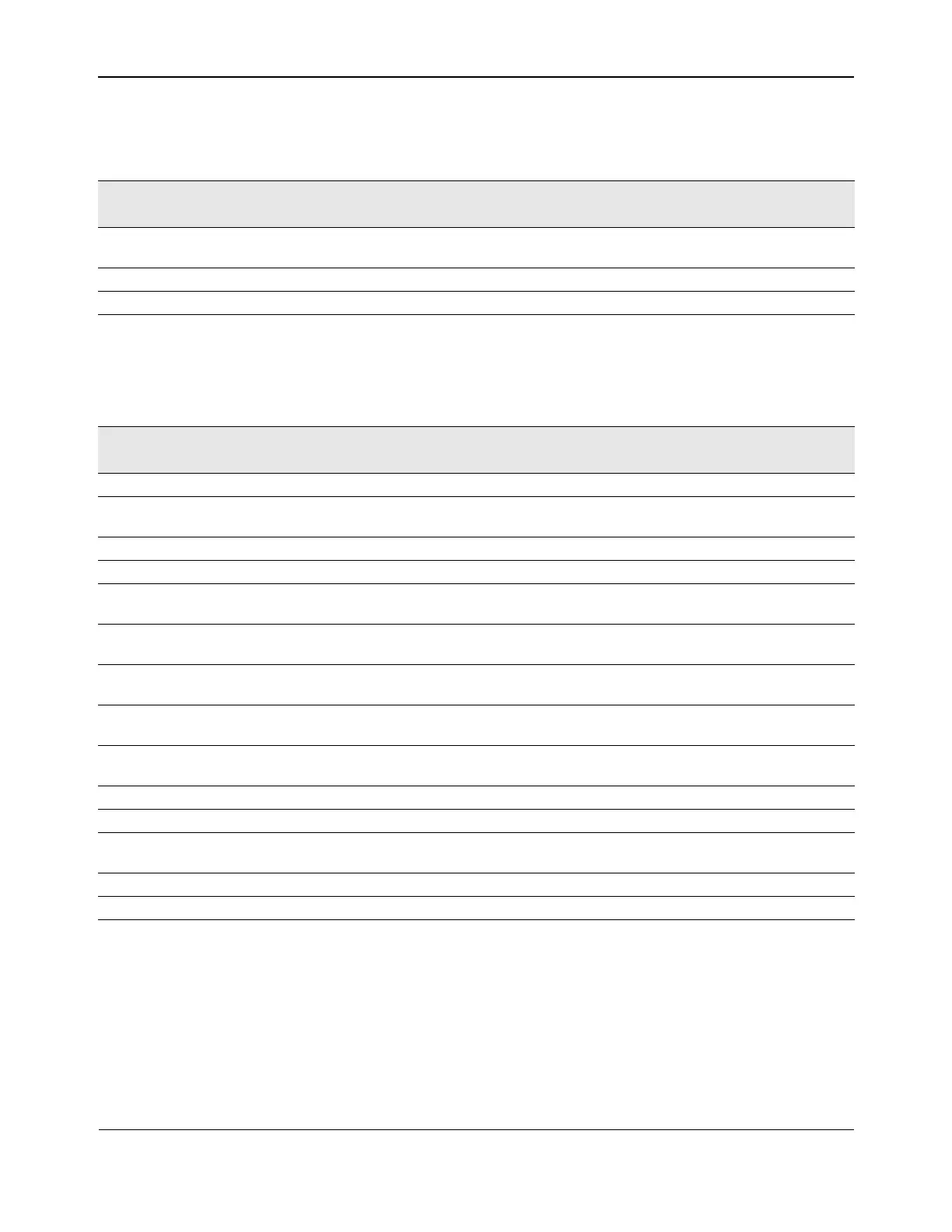

Advanced Error Reporting Enhanced Capability Header (offset:

0x100)

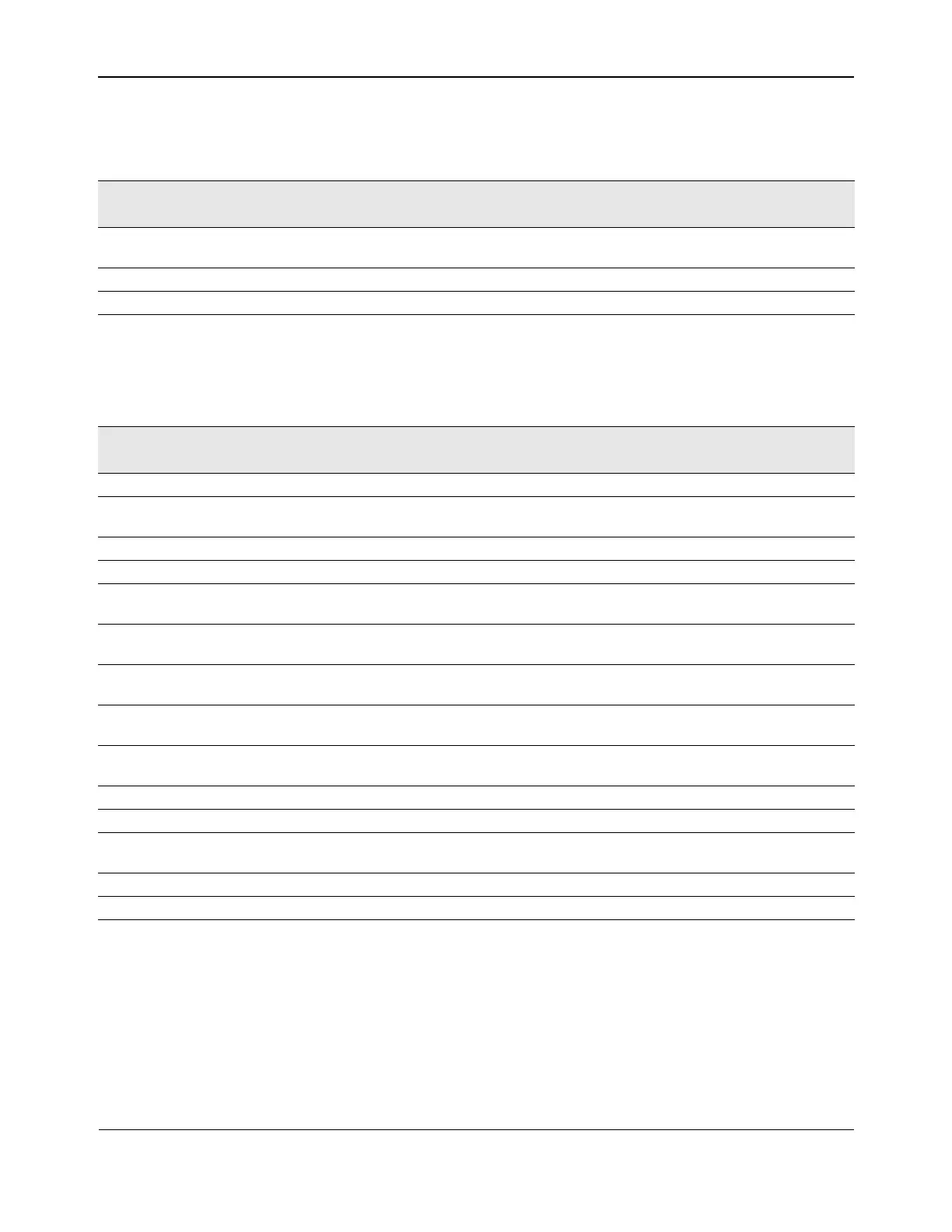

Uncorrectable Error Status Register (offset: 0x104)

This register is reset by Hard Reset.

Name Bits Access

Default

Value

Description

PCI Express Extended

Capability ID

15:0 RO 0x0001 Extended Capability ID for the Advanced Error

Reporting Capability is 0001h

Capability Version 19:16 RO 0x1 –

Next Capability Offset 31:20 RO 0x13C Pointer to the Virtual Channel Capability Structure

Name Bits Access

Default

Value

Description

Reserved 31:21 RO 0 –

Unsupported Request Error

Status

20 RW1CS 0 This bit is set when an unsupported request error

occurs.

ECRC Error Status 19 RW1CS 0 This bit is set when an ECRC error occurs

Malformed TLP Status 18 RW1CS 0 This bit is set when a Malformed TLP error occurs.

Receiver Overflow Status 17 RW1CS 0 This bit is set when a Receiver Overflow error

occurs.

Unexpected Completion

Status

16 RW1CS 0 This bit is set when an Unexpected Completion

error occurs.

Completer Abort Status 15 RW1CS 0 This bit is set when a completer Abort error

occurs.

Completion Timeout Status 14 RW1CS 0 This bit is set when completion timeout error

occurs.

Flow control Protocol Error

Status

13 RW1CS 0 This bit is set when a Flow control protocol error

occurs.

Poisoned TLP Status 12 RW1CS 0 This bit is set when a Poisoned TLP error occurs

Reserved 11:5 RO 0 –

Data Link Protocol Error

Status

4 RW1CS 0 This bit is set when a Data Link Protocol error

occurs.

Reserved 3:0 RO 0 –

Training Error Status 0 RW1CS 0 This bit is set when a training error occurs.

Loading...

Loading...