GRC RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 471

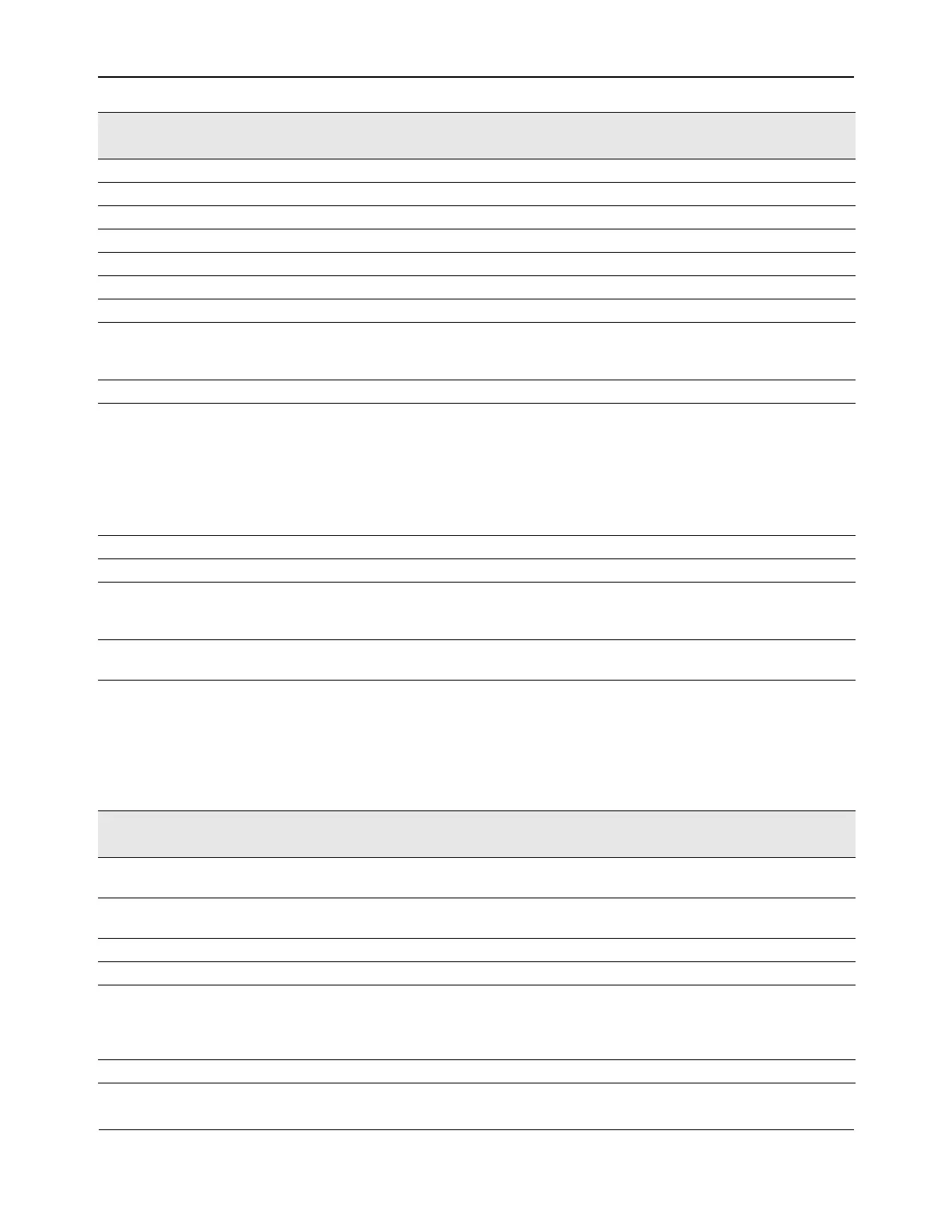

Miscellaneous Local Control Register (offset: 0x6808)

The Miscellaneous Local Control register is used to control various functions within the device. All bits are set

to zero (i.e. disabled) during reset.

ID4 27 RO ID4 Bond ID 4

Reserved 26 RW 0 –

Reserved 25 RW 0 –

Reserved 24 RW 0 –

Reserved 23 RW 0 –

Reserved 22 RW 0 –

Reserved 21 RW 0 –

Powerdown 20 RW 0 Setting this bit will power down the device (power

consumption is ~20 mW). This bit is cleared by

PCI reset.

PME EN State 19 RO 1 State of PME Enable for this device.

Power State 18:17 RO 0 Indicates the current power state of the device.

00b: D0

01b: D1

02b: D2

03b: D3

This PowerState mirrors the PMSCR register

Bond ID 16:13 RO ID 3:0 Bond ID

Reserved 12:8 RO 0 –

Timer Prescaler 7:1 RW 1111111b Local Core clock frequency in MHz, minus 1,

which should correspond to each advance of the

timer. Reset to all 1.

GRC Reset 0 RW 0 Write 1 to this bit resets the CORE_CLK blocks

in the device. This is a self-clearing bit.

Name Bits Access

Default

Value

Description

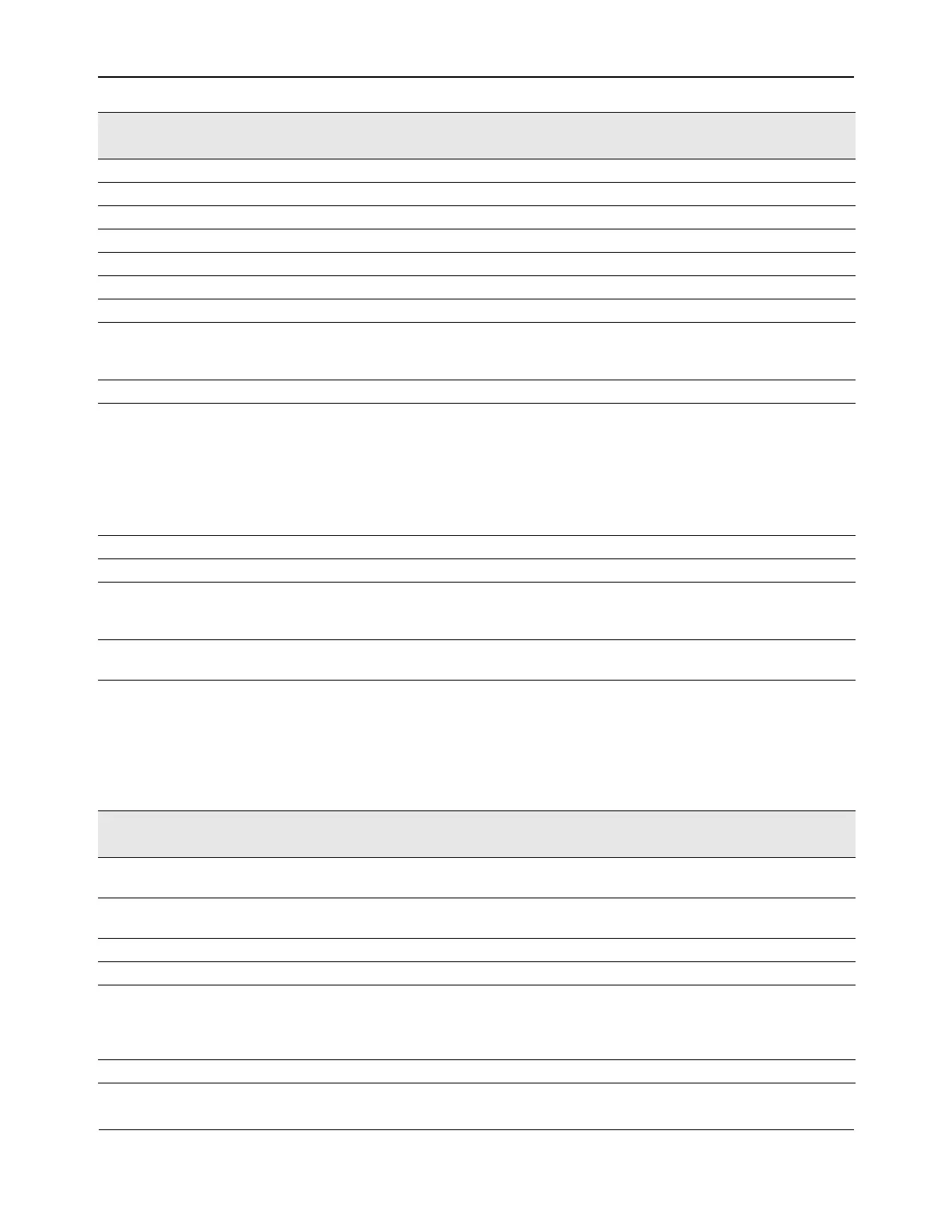

Enable Wake On Link Up 31 RW 0 When set, the chip drives the PME when the link

is up.

Enable Wake On Link Down 30 RW 0 When set, the chip drives the PME when the link

is down.

Disable Traffic LED fix 29 RW 0 Set to disable Traffic LED Fix.

Reserved 28:27 RO 0 –

PME Assert 26 RW 0 When set, the PME Status bit in the PMSCR

register is forced high. If PME Enable is also set,

the PME signal will activate. This register bit is

write-only and self-clearing after write.

Reserved 25 RO 0 –

Name Bits Access

Default

Value

Description

Loading...

Loading...