PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 282

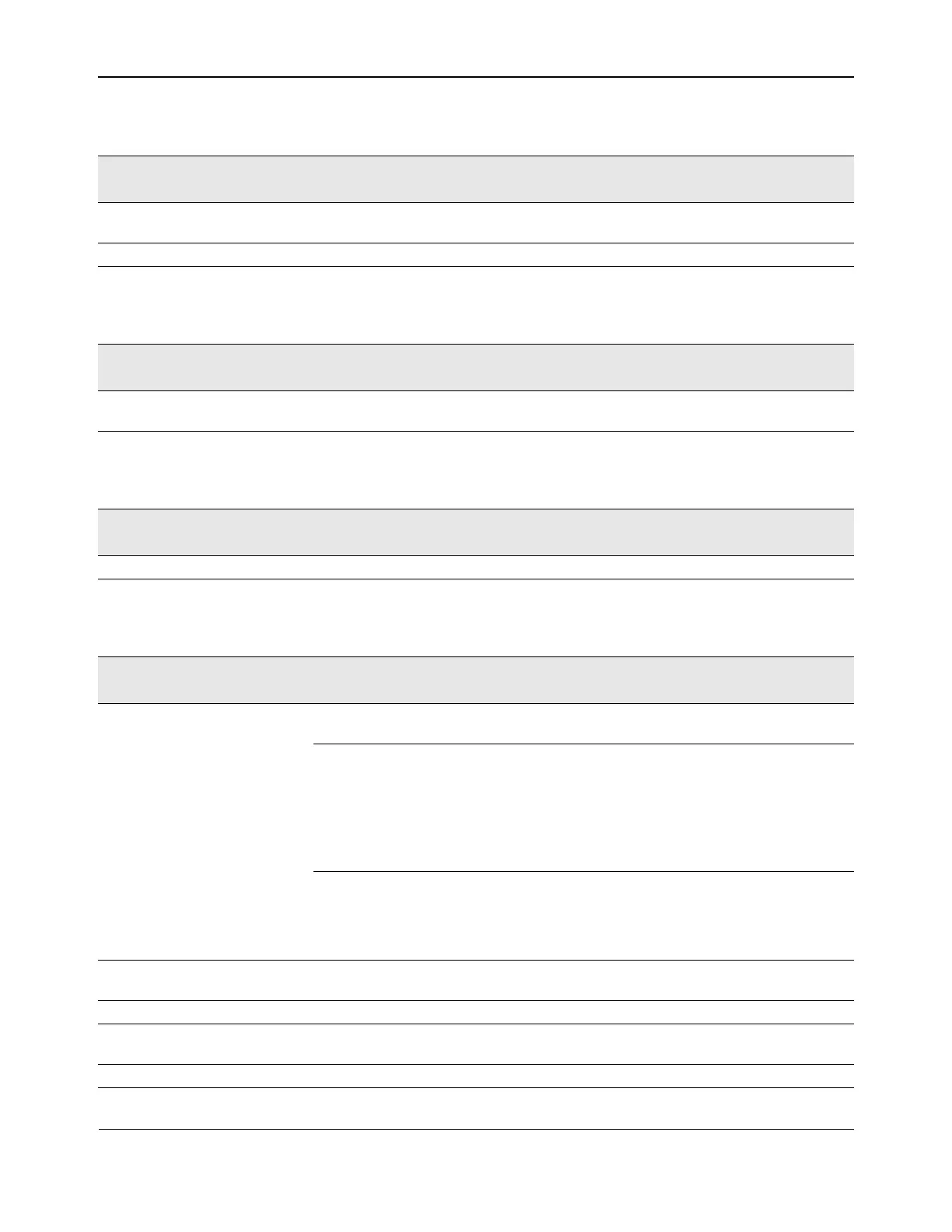

MSI Lower Address Register (offset: 0x5C)

MSI Upper Address Register (offset: 0x60)

MSI Data Register (offset: 0x64)

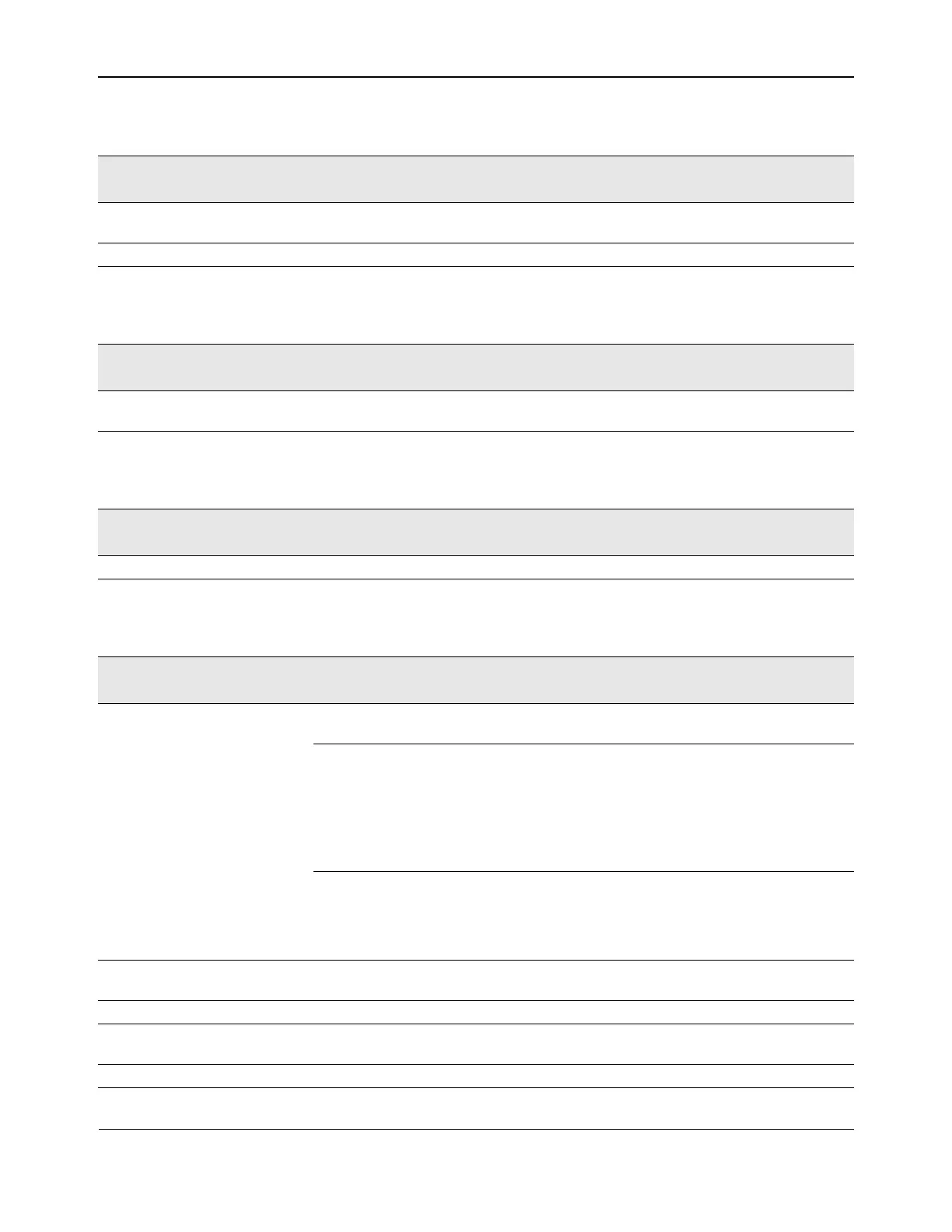

Miscellaneous Host Control Register (offset: 0x68)

Name Bits Access

Default

Value

Description

MSI Lower

Address

31:2 RW Unknown MSI Lower Address

Reserved 1:0 RO 0 –

Name Bits Access

Default

Value

Description

MSI Upper

Address

31:0 RW Unknown MSI Upper Address

Name Bits Access

Default

Value

Description

MSI Data 15:0 RW Unknown MSI Data

Name Bits Access

Default

Value

Description

ASIC Rev ID 31:28 R Product ID

input

0xF: Indication that BCM5718 family follows new

PRODUCT/REV ID mapping

27:24 R ASIC Rev

Input

External All Layer Revision ID.

These bits will reflect in offset 8-bit mapping

description:

0x0: A

0x1: B

0x2: C

23:16 R ASIC Rev

Input

Metal Rev Number

0x0: 0

0x1: 1

0x2: 2

Enable TLP Minor Error

Tolerance

15 RW 0 Set this bit to enable TLP minor error tolerance

(ATTR/TC/LOCK command)

Log Header Overflow 14 RW 0 Set this bit to enable log header due to overflow

Boundary check 13 RW 0 Set this bit to enable crossing 4 KB boundary

check

Byte enable Rule Check 12 RW 0 Set this bit to enable the byte enable rule check

Loading...

Loading...