PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 306

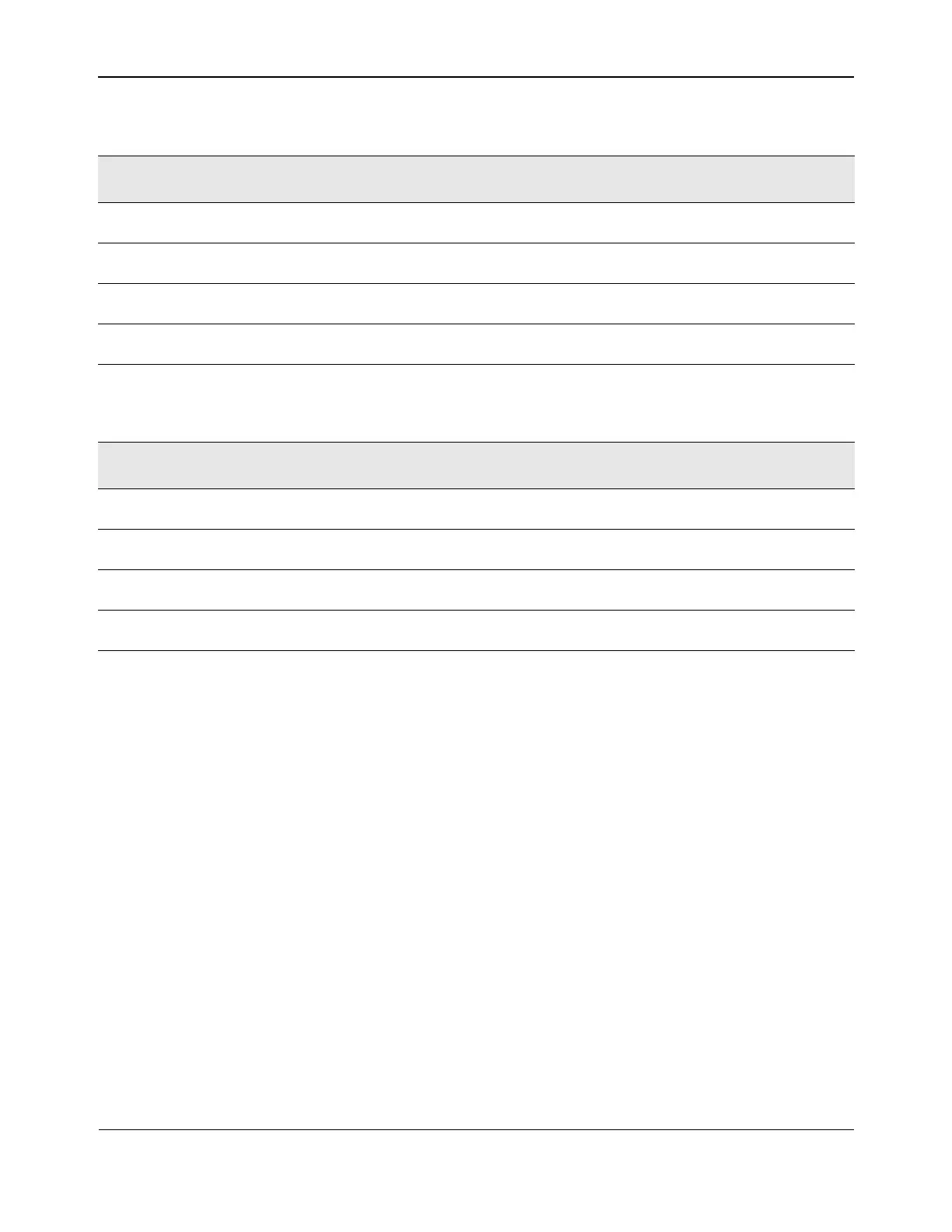

Header Log Register (offset: 0x124)

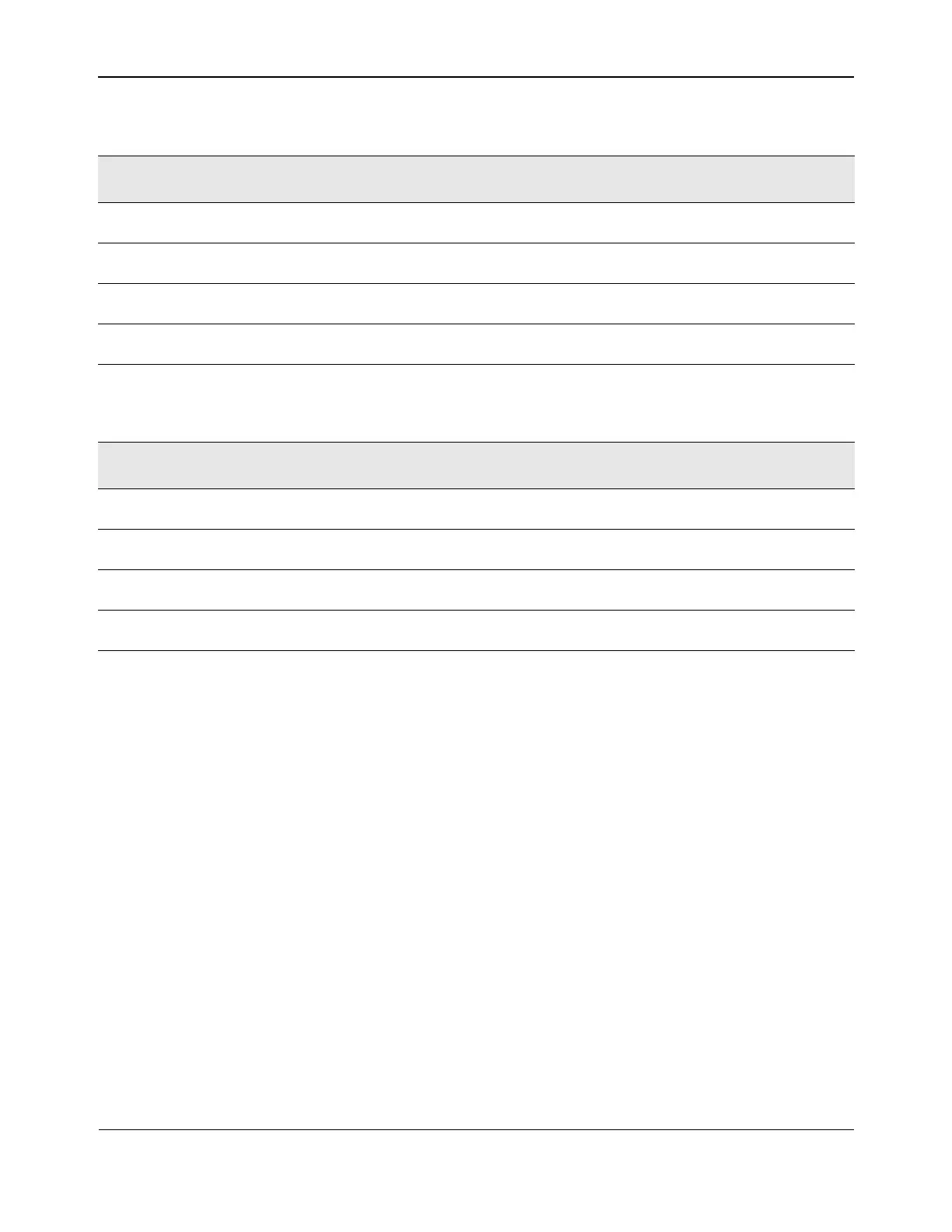

Header Log Register (offset: 0x128)

Interrupt mail box (High Priority Mailbox) Register

(offset: 0x200 – 0x21c)

This mailbox serves two functions. When the host writes it, the interrupt (IntA) is cleared. It is also used by the

Host Coalescing engine to determine if the host is in the interrupt handler. If it is non-zero this indicates the host

is in the interrupt handler. If it is zero this indicates the host is not in the interrupt handler. The Host Coalescing

engine uses this information to determine which set of coalescing parameters it should use.

General mail box (High Priority Mailbox)

Register (offset: 0x220–0x25c)

Reload Statistics mail box (High Priority Mailbox)

Register (offset: 0x260–0x264)

Name Bits Access

Default

Value

Description

Header Byte 8 31:24 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 9 23:16 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 10 15:8 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 11 7:0 ROS – The TLP header of the transaction that has

incurred a failure.

Name Bits Access

Default

Value

Description

Header Byte 12 31:24 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 13 23:16 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 14 15:8 ROS – The TLP header of the transaction that has

incurred a failure.

Header Byte 15 7:0 ROS – The TLP header of the transaction that has

incurred a failure.

Loading...

Loading...