MSI-X PlumbingBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 250

Status-Block [1–16] Status Word Format (Multivector IOV):

• Bit [0]: Update-Bit

• Bit [1]: Link Status Change

• Bits [31:1]: Resvd–always 0x0

MSI-X Capability Structure

MSI-X requires that its device-resident data structures or registers be addresses over BARs, as opposed to MSI,

which declares its device structure addresses directly in related configuration registers. The are certain

restrictions related to the BARs:

• If a BAR is shared with MSI-X for other device purposes, the MSI-X region must be isolated within a 4 KB

naturally aligned region. Or, the MSI-X structures may be placed in their own captive BARs.

• MSI-X has been placed in it own set of BARs: BAR4 and BAR5 (64-bit).

• Each PCIe Function of the BCM5718 family, that is Function0 and Function1, advertises availability of their

BAR4 and BAR5 as MSI-X BARs. This is done via the MSI-X Capability structure.

The MSI-X Capability structure is implemented inside the EP-RC core. It points to two structures that must be

implemented inside a device: the MSI-X Table and a Pending Bit Array (PBA). There is also a Message Control

Register. The Capability structure is shown in Ta b l e 98 .

The BIR bits point to the BAR registers that a device function uses to base the respective data structures. In the

BCM5718 family, both BIRs have a hard-wired value of 0x4, which implies BAR4 and BAR5.

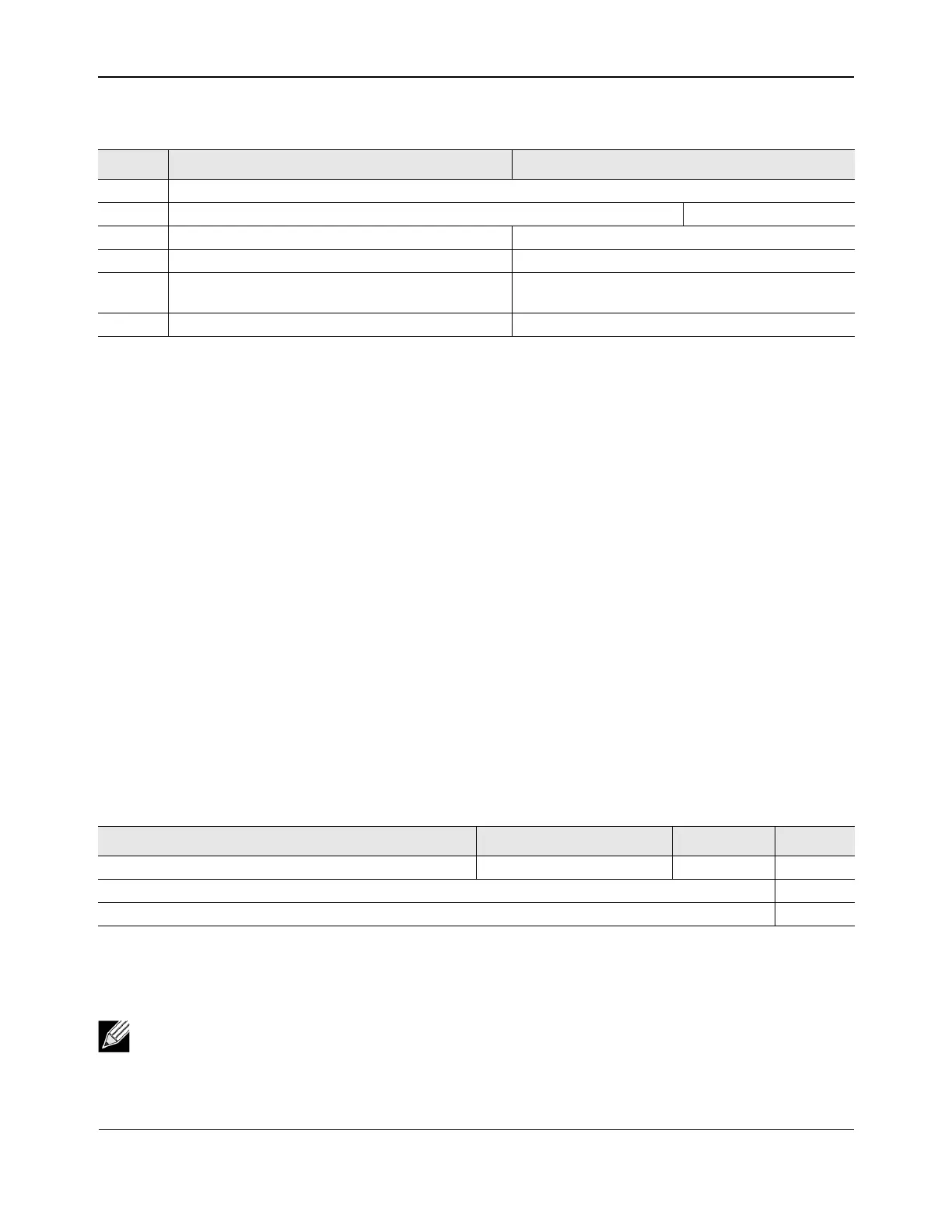

Table 97: Status Block [1 N 16] Format (MSI-X Multivector IOV Mode)

offset 3116 150

0x00 Status Word

0x04 [31:8] Reserved 0x0 [7:0] Status Tag

0x08 RBD[N] Standard Producer Ring Consumer Index Reserved 0x0

0x0C Reserved 0x0 Reserved 0x0

0x10 Send BD [N] Consumer Index (IF Multiple Send

queue ELSE 0x0)

Receive Return Ring [N] Producer Index

0x14 Reserved 0x0 RBD [N] Jumbo Producer Ring Consumer Index

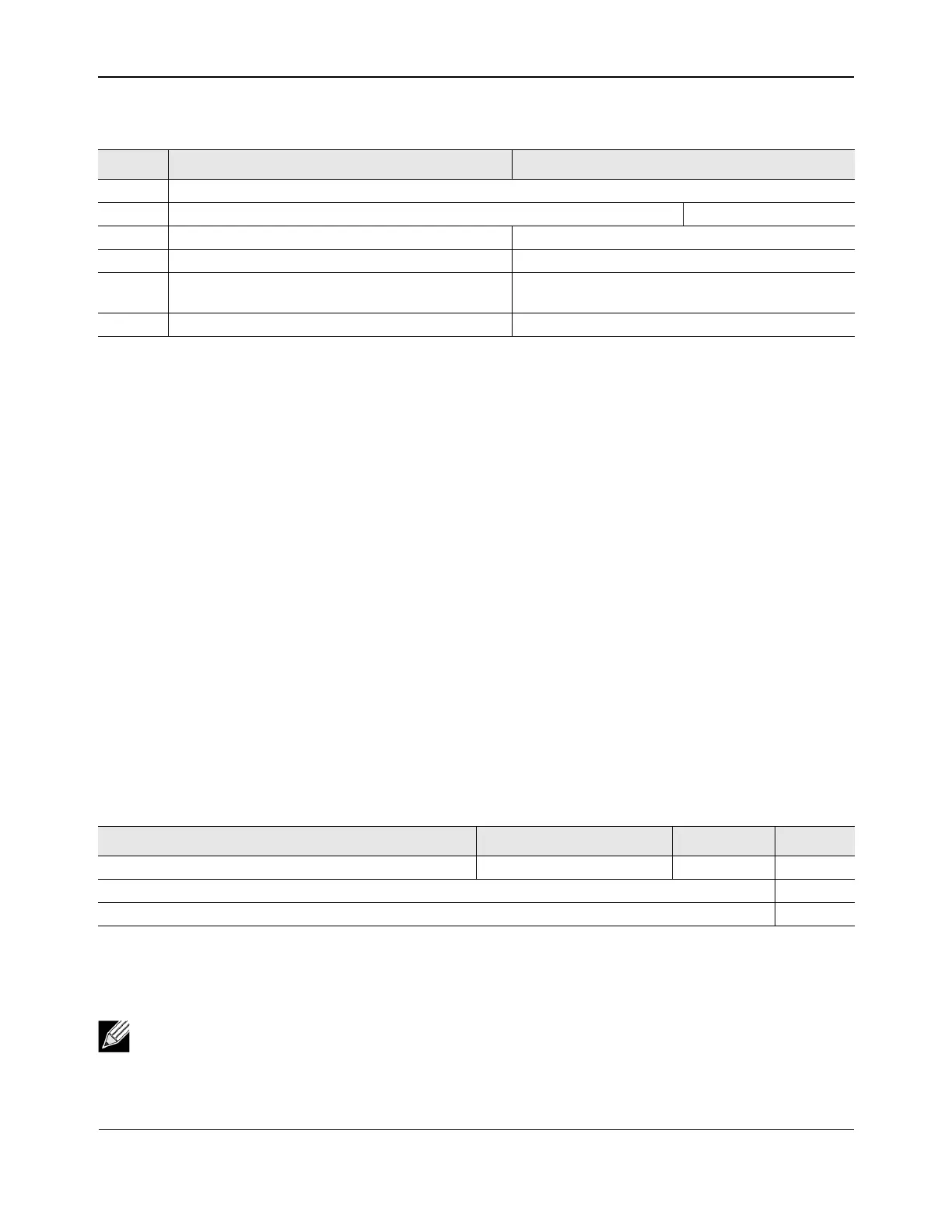

Table 98: MSI-X Capability Structure

3116 158 73 20

Message Control Reg Next Pointer Capability ID –

MSI-X Table Offset Table BIR

PBA Offset PBA BIR

Note: BAR4 and BAR5 must support 8/16- and 32-bit accesses from the host. However, unaligned

16/32-bit access support are not required.

Loading...

Loading...