SerDes PHY Register DefinitionsBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 550

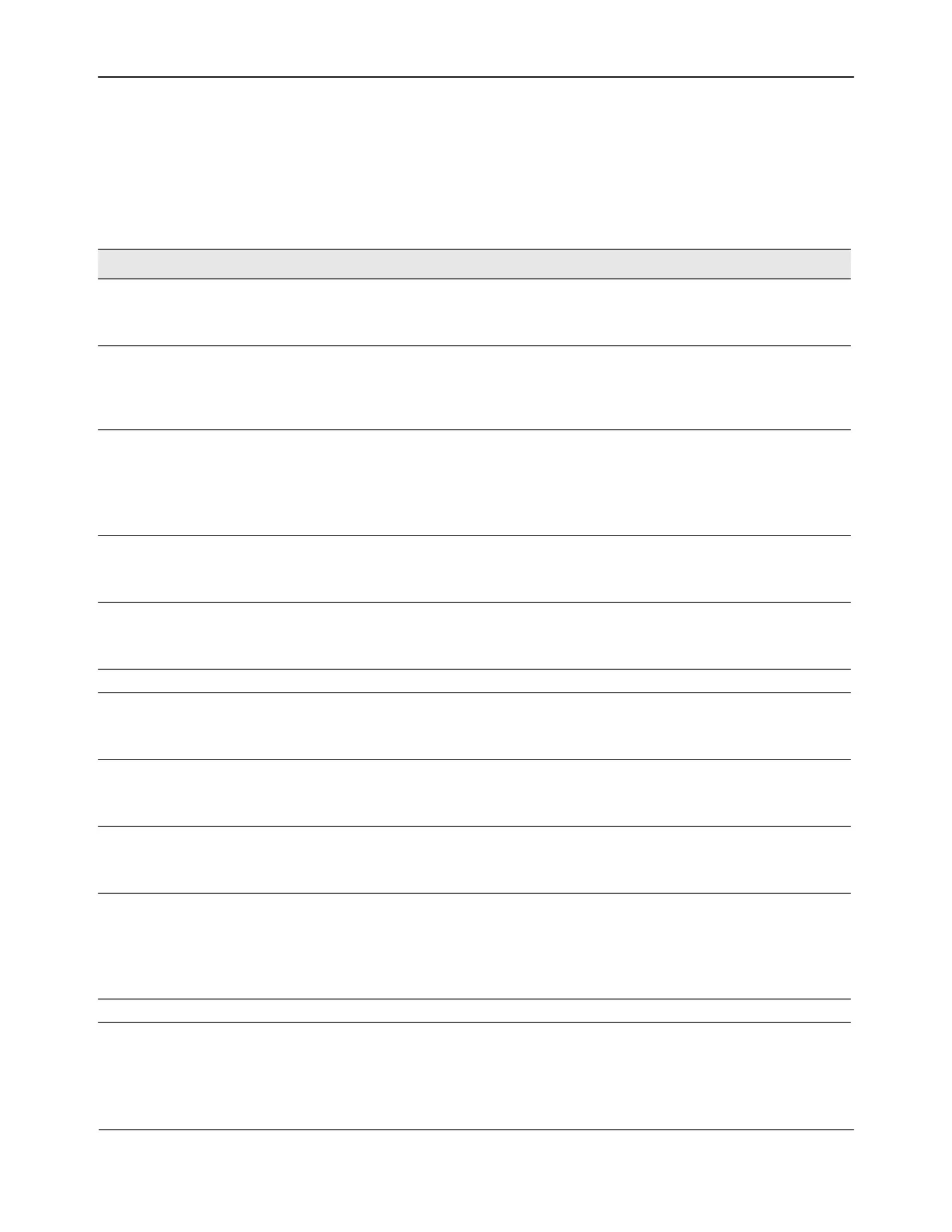

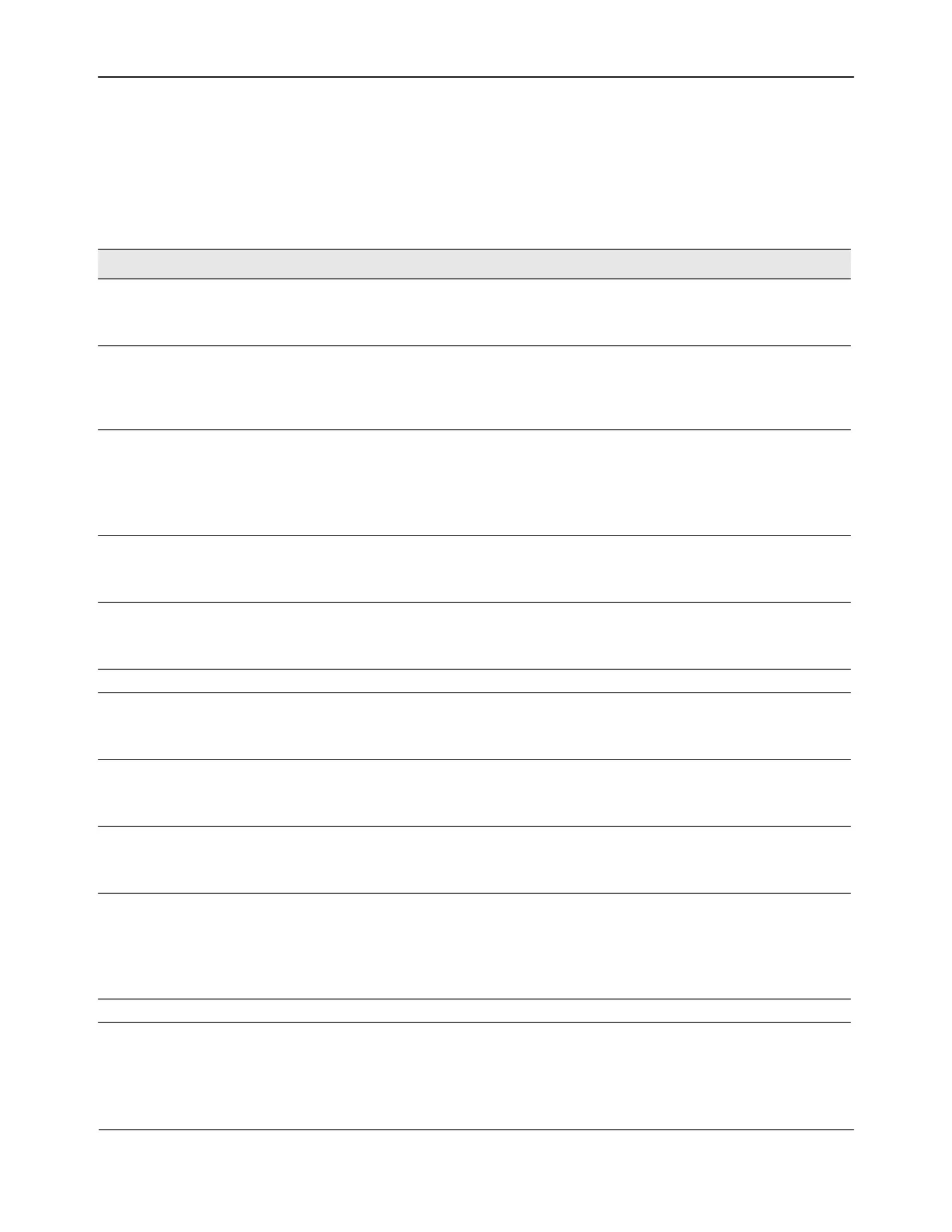

MII Control

Register Description: MII Control Register.

Register Offset: 0x0 at Block 0

Table 126: MII Control

Bits Name RW Description Default

15 RST_SW RW PHY Reset

0 = Normal Operation

1 = Reset

0

14 LOOPBACK RW Local loopback, data is looping back at the PHY before

going out to the wire.

0 = Normal operation

1 = Loopback enable

0

13 SPD[0] RW Bit[0] of manual Speed[1:0] in SGMII mode only. This field

is ignored in 1000Base-X operation.

1X = 1000 Mbps

01 = 100 Mbps

00 = 10 Mbps

0x0

12 AN_EN RW Auto-negotiation enable

0 = Disable

1 = Enable AN

1

11 PWRDN RW Power down GE SerDes

0 = Normal operation

1 = Power-down the SerDes PHY

0

10 RESERVED RO Reserved write 0, ignore read 0

9 RESTART_AN RW Restart Auto-negotiation process

0 = Normal operation

1 = Restart AN

0

8 FDX RW Duplex mode

0 = Half duplex

1 = Full duplex

0

7 COL_TEST_EN RW Collision test enable

0 = Normal operation

1 = Collision test

0

6 SPD[1] RW Bit[1] of manual Speed[1:0] in SGMII mode only. This field

is ignored in 1000Base-X operation.

1X = 1000 Mbps

01 = 100 Mbps

00 = 10 Mbps

1

5:0 RESERVED RO Reserved write 0, ignore read. 0x0

Loading...

Loading...