Receive Data and Receive BD Initiator Control RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 364

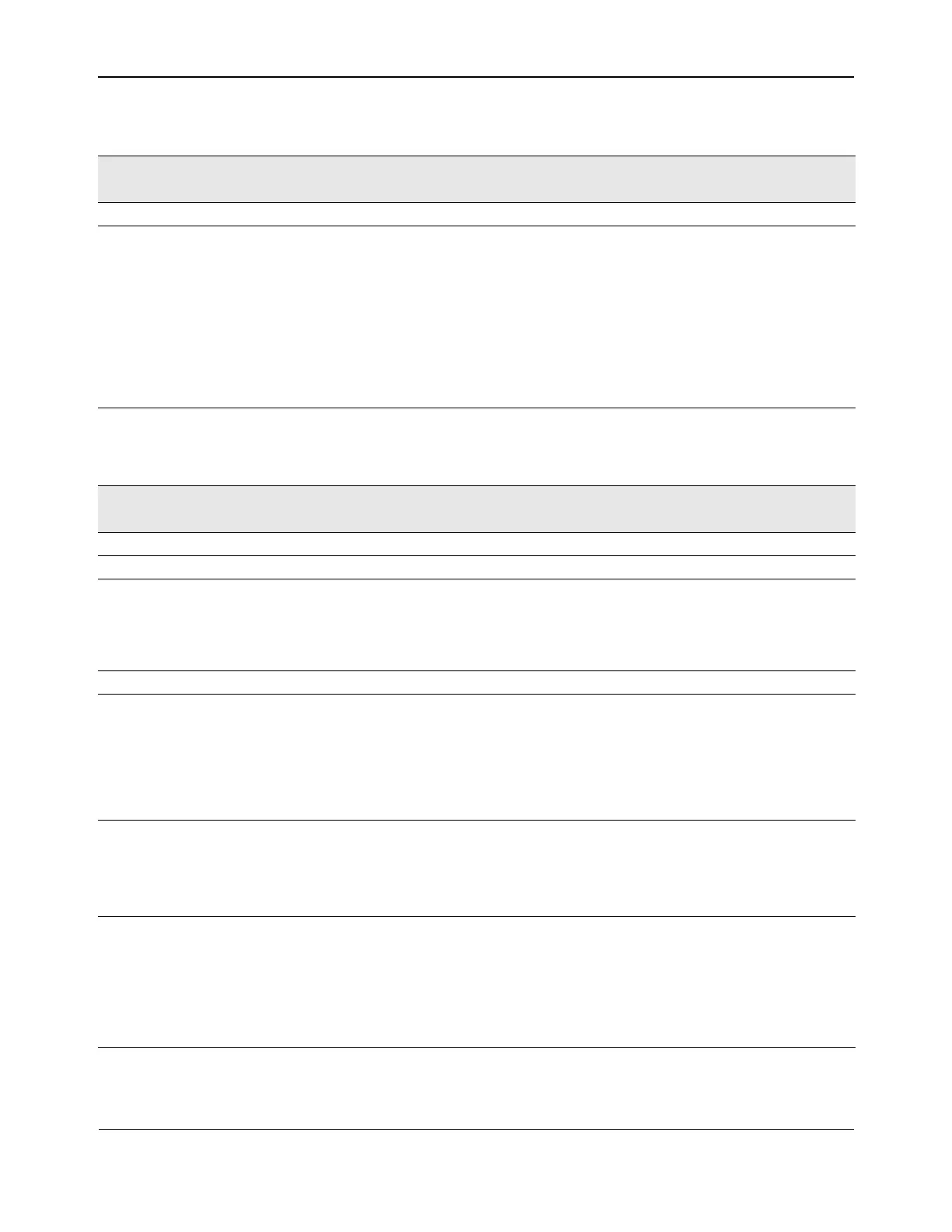

VRQ Status Register (offset: 0x240C)

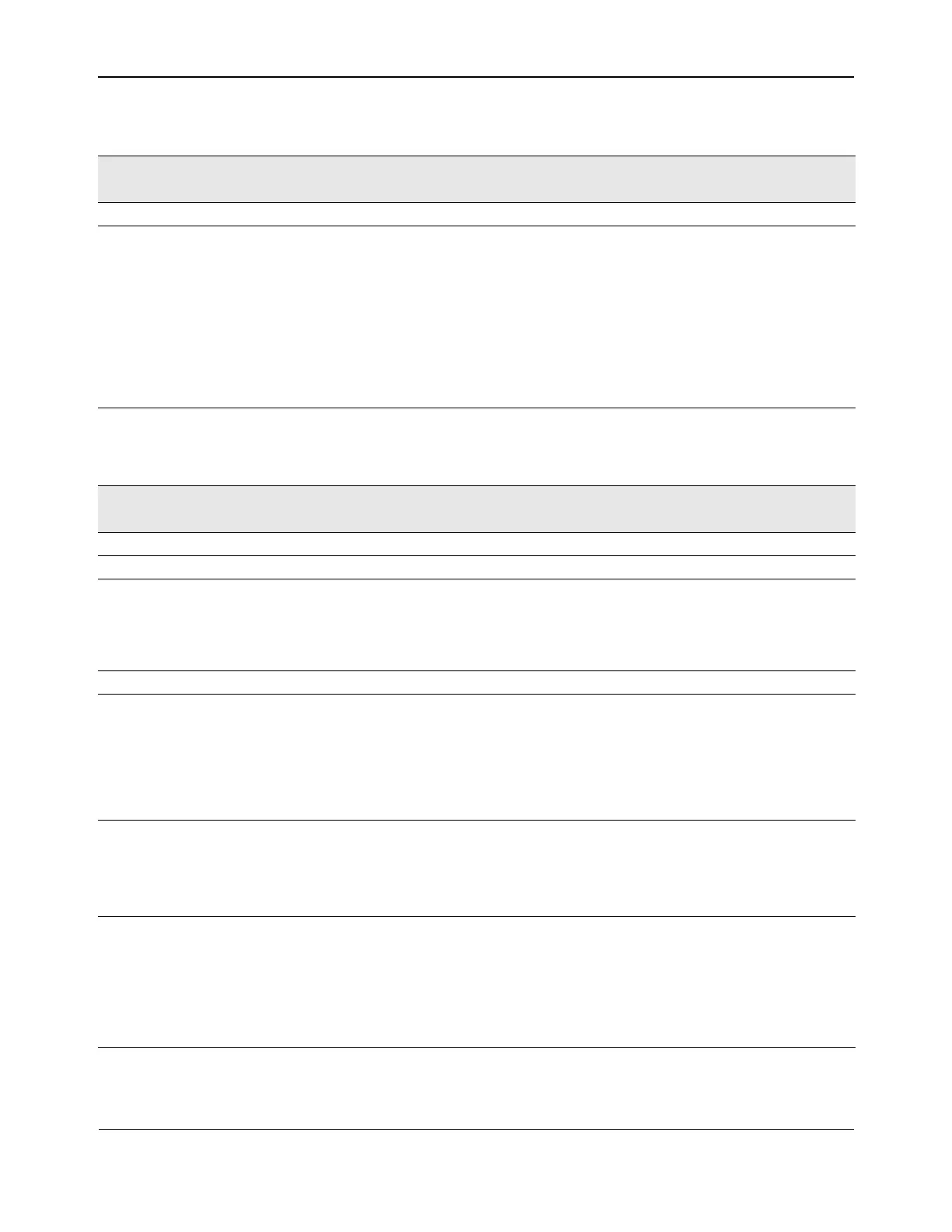

VRQ Flush Control Register (Offset: 0x2410)

Name Bits Access

Default

Value

Description

Legacy 31:17 RU 0x0 Unused

VRQ Active Bit-Map 16:0 RW 0x0 A position of the Bit-Map shows a 1, in case the

VRQ is currently enabled or recently disabled

and is at the verge of being flushed, and thus

there could possibly be associated traffic inside

the chip.

A bit-position shows 0, when a VRQ is

completely disabled and there is no traffic

whatsoever associated with it either inside the

chip or in the PCIe link between the chip and the

Root-Complex.

Name Bits Access

Default

Value

Description

S/W flush IOV vector 31:15 RW 0x0 S/W Flush vector [16:0].

Reserved 14:9 RW 0x0 Reserved

S/W flush reset request 8 RW/SC 0x0 Software writing 1 to this bit to force an internal

index reset request. Bit-8 combining with [31:15]

bit-map indicates which IOV index group to be

reset. The function is identical to bit-1 hardware

flush reset. This bit is self-clear.

Reserved 7:4 RW 0x0 Reserved

VRQ hardware flush drop

enable

3 RW 0x0 1: Enable hardware drop packet function

immediately when the IOV enable bits are

disabled from driver. This bit will force RDI and

WDMA engines to place the incoming packets

into drop queue when the IOV enable bit is

disabled in EMAC for that particular IOV child

process.

VRQ status update and

interrupt enable

2 RW 0x0 1: Enable hardware triggered host status

interrupt and status block update request.

RDI engine will generate a single pulse request

signal to HC alone with current IOV status vector

value for status block update.

VRQ hardware flush reset

enable

1 RW 0x0 1: Enable hardware local index reset feature

when VRQ flush timer expires.

RDI engine will generate a single pulse clear

request along with current IOV status [16:0]

vector to various modules to clear local

maintained index values for that particular IOV

process.

Loading...

Loading...