PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 298

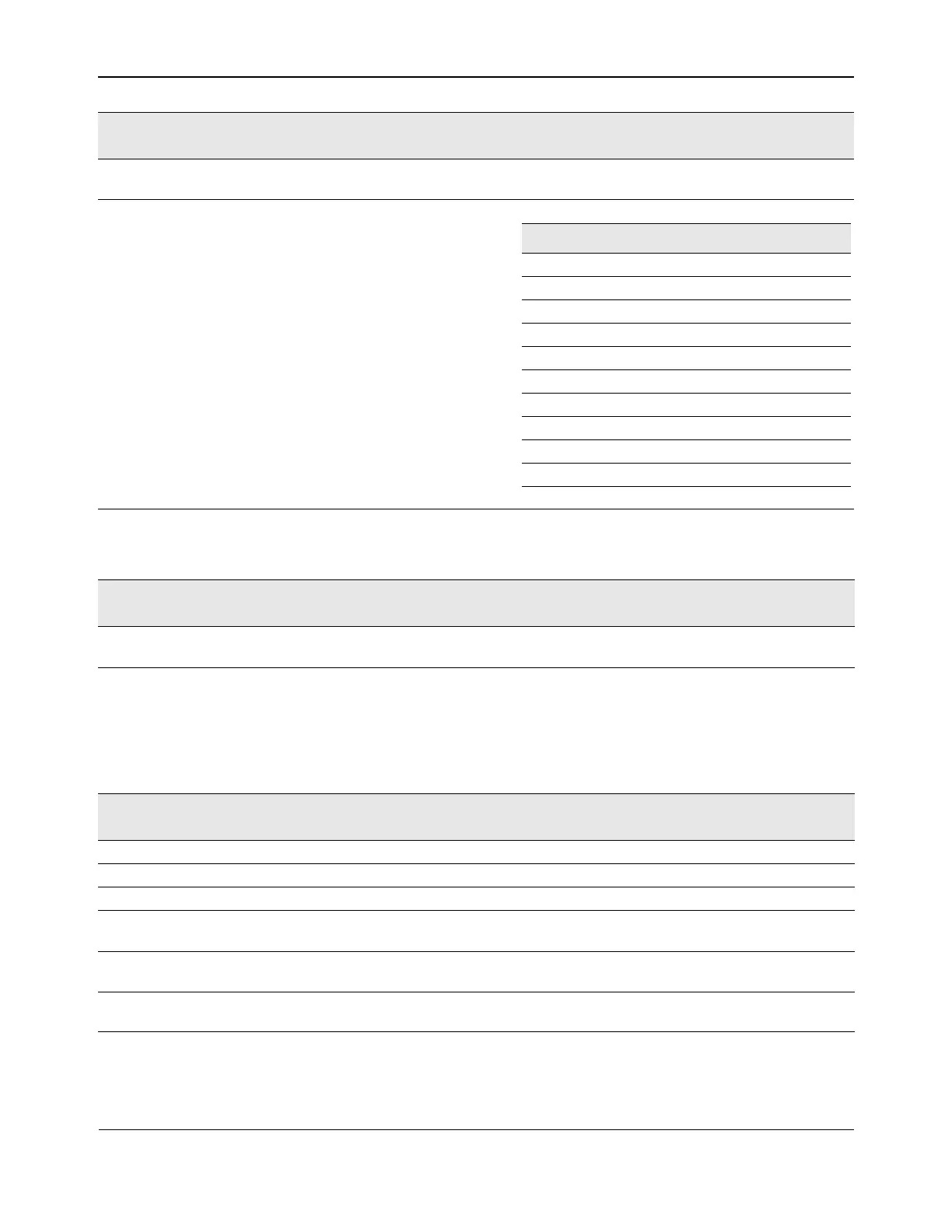

LINK_CAPABILITY_2 – 0xd8

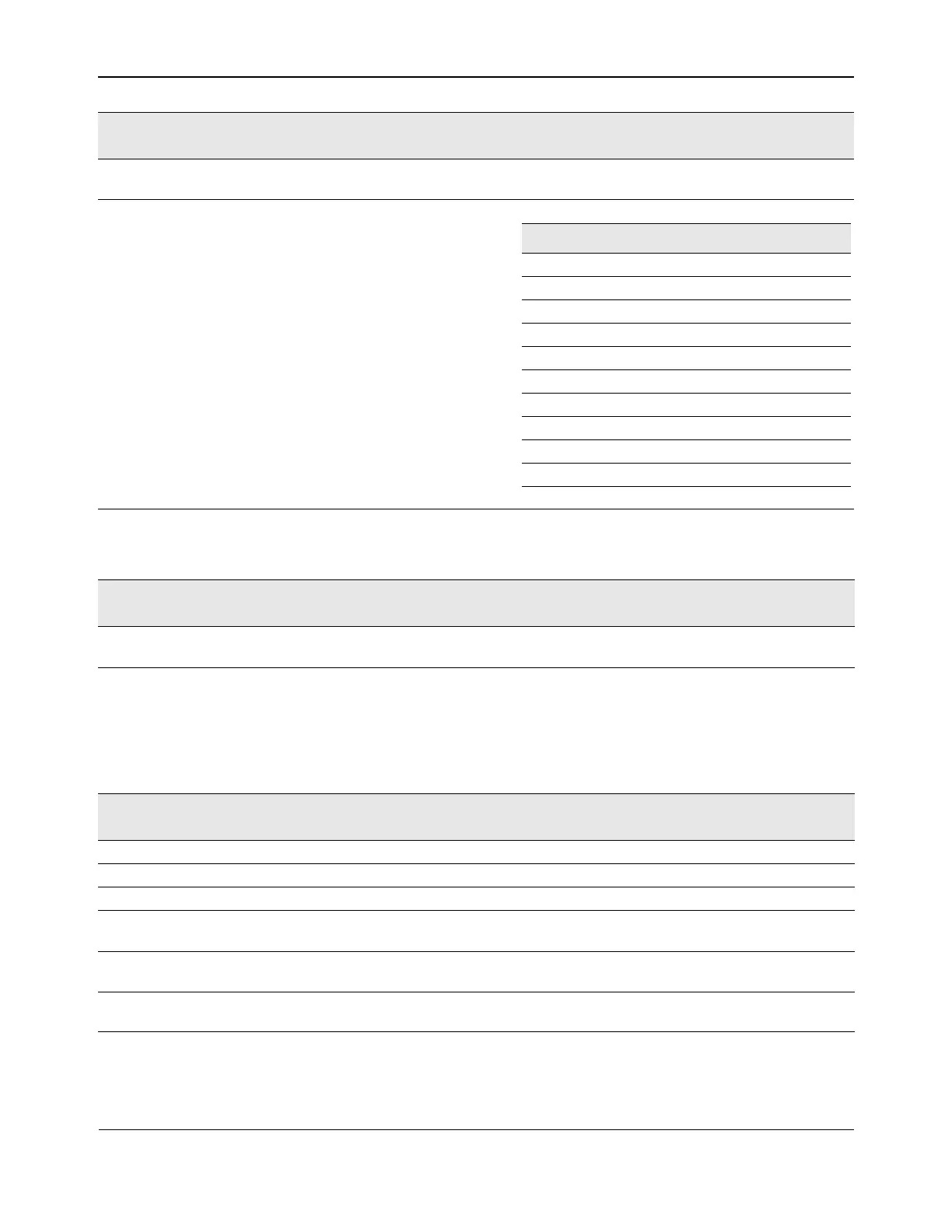

LINK_STATUS_CONTROL_2 – 0xdc

This register will be Read only by default, and will read all 0's to allow compliance with PCIE spec 1.1. To enable

this register, reset comply_pcie_1_1 bit in the register space to 0.

CMPL_TIMEOUT_DISABLE 4 RW 0 Completion Timeout Disable

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

CMPL_TIMEOUT_VALUE 3:0 RW 0

Name Bits Access

Default

Value

Description

LINK_CAPABILITY_2 31:0 RO 0 Placeholder for Gen2 Path=

i_cfg_func.i_cfg_private

Name Bits Access

Default

Value

Description

LINK_STATUS_2 31:17 RO 0 Placeholder for Gen2

CURR_DEEMPH_LEVEL 16 RO 0 curr_deemph_level Path = pl_top

Unused0 15:13 RO 0 –

CFG_COMPLIANCE_DEEM

PH

12 RW 0 Compliance De-emphasis.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

CFG_COMPLIANCE_SOS 11 RW 0 Compliance SOS.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

CFG_ENTER_MOD_

COMPLIANCE

10 RW 0 Enter Modified Compliance.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

Name Bits Access

Default

Value

Description

Value Name Description

0 50MS 50ms

1 100US 100us

2 10MS 10ms

3 55MS 55ms

4 210MS 210ms

5 900MS 900ms

63_5S3.5s

13S 13s

864S64s

255 – end_of_table

Loading...

Loading...