SerDes PHY Register DefinitionsBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 549

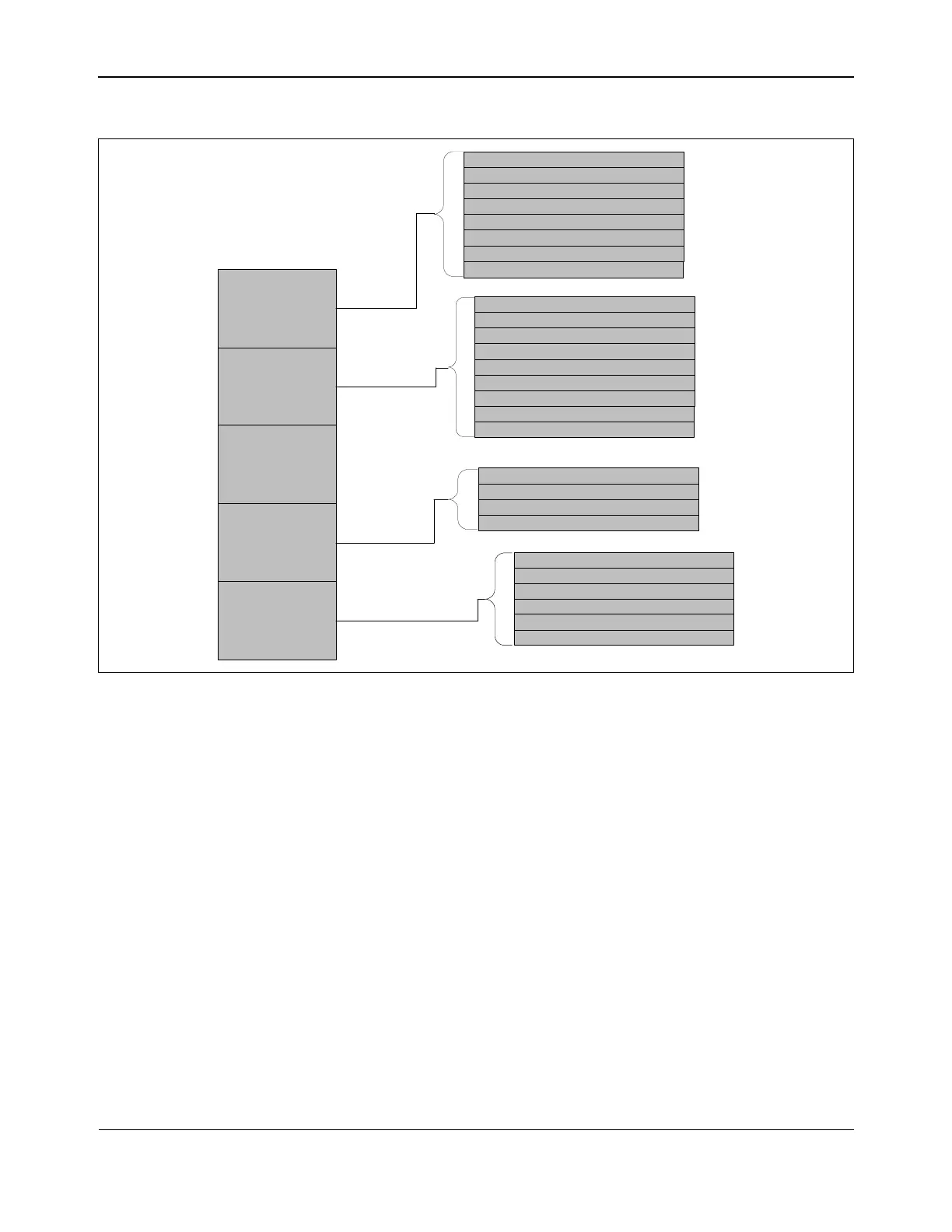

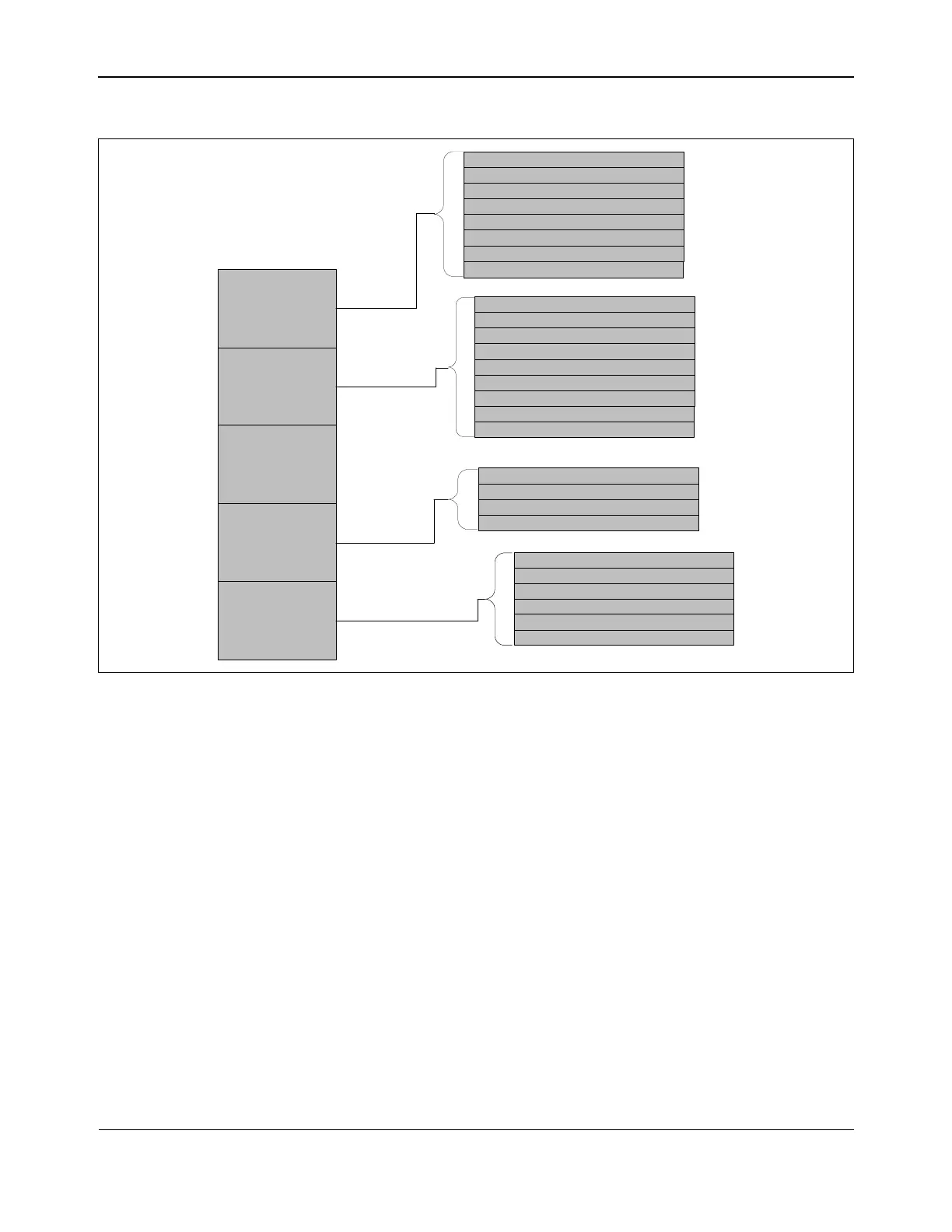

Figure 55: SerDes PHY Register Map

Serdes PHY Registers

mapping table

MII Registers

Block Address 0

00h to 0Fh

IEEE Defined

MII Registers

Block Address 0

10h to 1Fh

Digital Defined

MII Registers

Block Address 1

10h to 1Fh

SerDes ID Defined

MII Registers

Block Address 2

10h to 1Fh

FX100 Digital Defined

MII Registers

Block Address 3

10h to 1Fh

Analog Defined

00h – MII Control Reg

01h – MII Status Reg

02h – PHY ID MSB Reg

03h – PHY ID LSB Reg

04h – Auto-Neg Advertisement Reg

05h – Anto-Neg Link Partner Ability Reg

06h – Auto-Neg Expansion Reg

0Fh – IEEE Extended Status Reg

IEEE Defined

Registers

10h – 1000X Control1 Reg

11h – 1000X Control2 Reg

12h – 1000X Control3 Reg

13h – 1000X Control4 Reg

14h – 1000X Status1 Reg

15h – 1000X Status2 Reg

16h – 1000X Status3 Reg

Digital Defined

Registers

10h – FXControl1 Reg

11h – FXControl2 Reg

12h – FXControl3 Reg

13h – FXStatus1 Reg

FX100 Defined

Registers

10h – ANALOG_TX1 Reg

11h – ANALOG_TX2 Reg

12h – ANALOG_TXAMP Reg

13h – ANALOG RX1 Reg

14h – ANALOG_RX2 Reg

15h – ANALOG PLL Reg

Analog Defined

Registers

18h – GE_PRBS_CONTROL Reg

19h – GE_PRBS_STATUS Reg

Loading...

Loading...