PCI Configuration RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 290

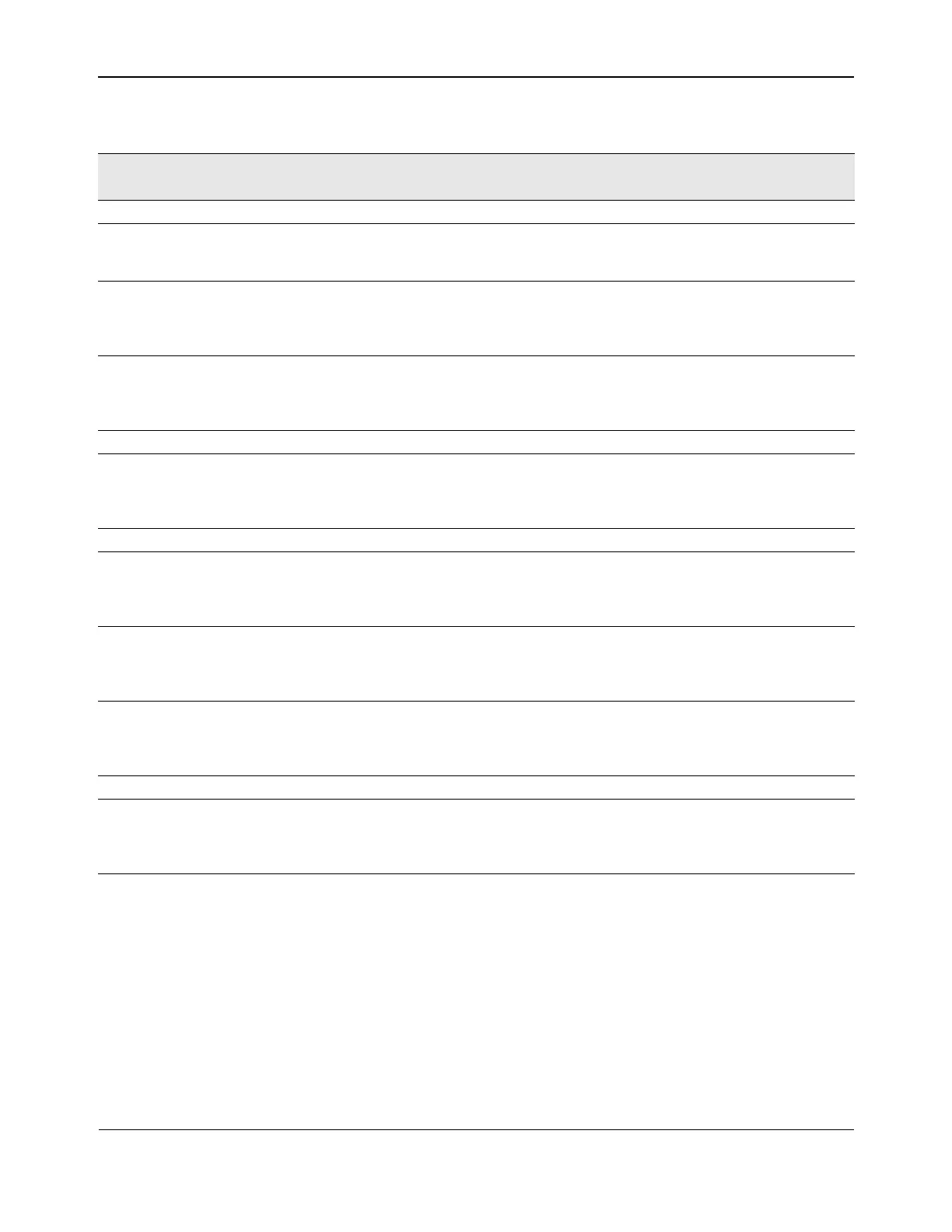

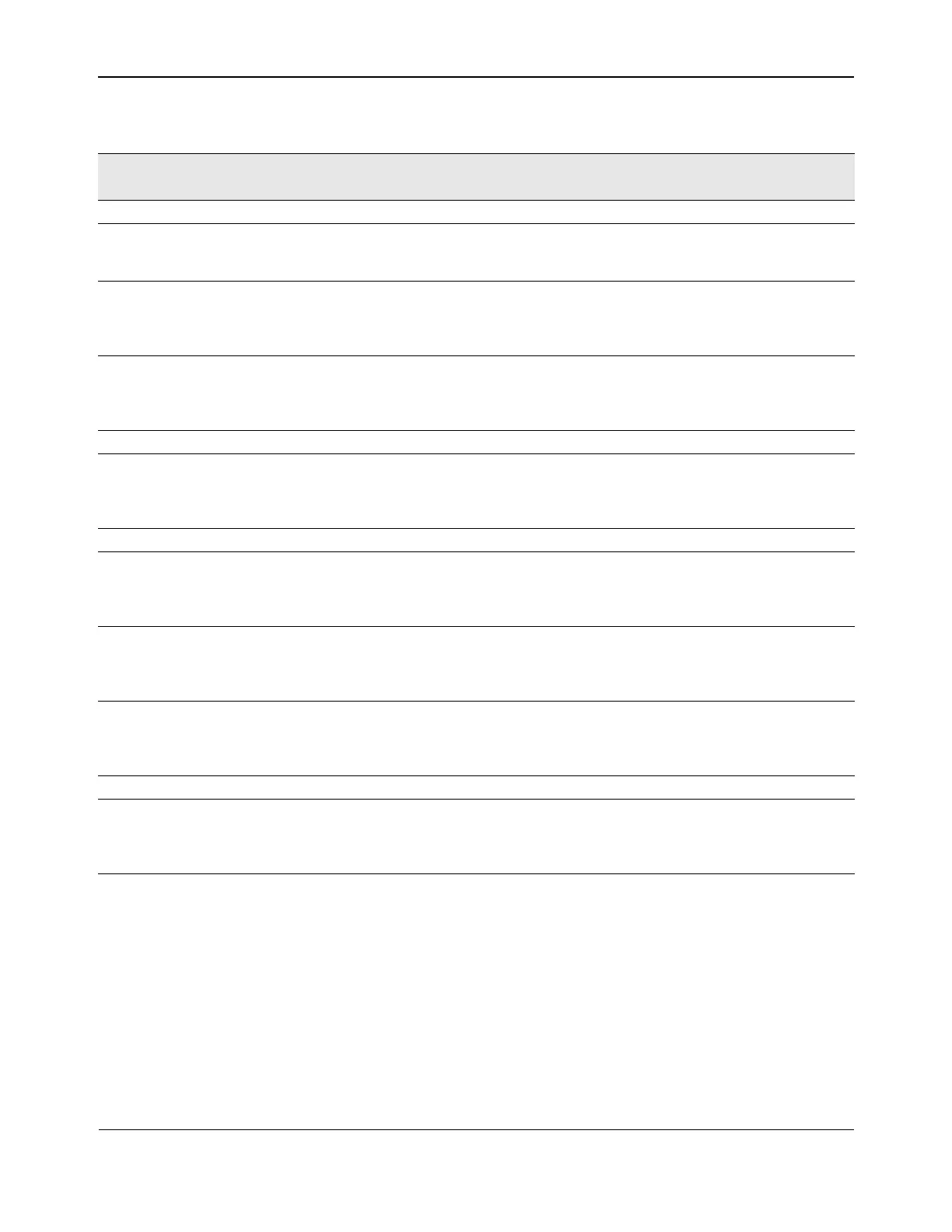

DEVICE_CAPABILITY – 0xb0

Name Bits Access

Default

Value

Description

unused3 31:29 RO 0 –

FLR_CAP_SUPPORTED 28 RO 0 FLR capability is advertized when flr_supported

bit in private device_capability register space is

set.

CAPTURED_SLOT_PWR_S

CALE

27:26 RO 0 Specifies the scale used for the Slot Power Limit

Value. It is set by the Set_Slot_Power_Limit

Message. This field is not set for Root ports

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

CAPTURED_SLOT_PWR_V

AL

25:18 RO 0 Specifies the upper limit on power supplied by

slot. It is set by the Set_Slot_Power_Limit

Message. This field is not set for Root ports.

Path= i_cfg_func.i_cfg_public.i_cfg_exp_cap

unused2 17:16 RO 0 –

ROLE_BASED_ERR_RPT 15 RO 0x1 Indicate device is conforming to the ECN, PCI

Express Base Specification, Revision 1.1., or

subsequent PCI Express Base Specification

revisions. Path= i_cfg_func.i_cfg_private

unused1 14:12 RO 0 –

L1_ACCEPTABLE_LATENCY 11:9 RO 0x6 Endpoint L1 Acceptable Latency. These bits are

programmable through register space. The bits

should be 0 for Root ports.

Path= i_cfg_func.i_cfg_private

L0S_ACCEPTABLE_LATENC

Y

8:6 RO 0x6 Endpoint L0s Acceptable Latency. These bits are

programmable through register space. The value

should be 0 for root ports.

Path= i_cfg_func.i_cfg_private

EXTENDED_TAG_SUPPOR

T

5 RO 0 Extended Tag Field Support. This bit is

programmable through register space. This

capability is not currently supported.

Path= i_cfg_func.i_cfg_private

unused0 4:3 RO 0

MAX_PL_SIZE_SUPPORTE

D

2:0 RO 0x1 Max Payload Size Supported. These bits are

programmable from the register space and default

value is based on define in version.v file. Path=

i_cfg_func.i_cfg_private

Loading...

Loading...