Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-27

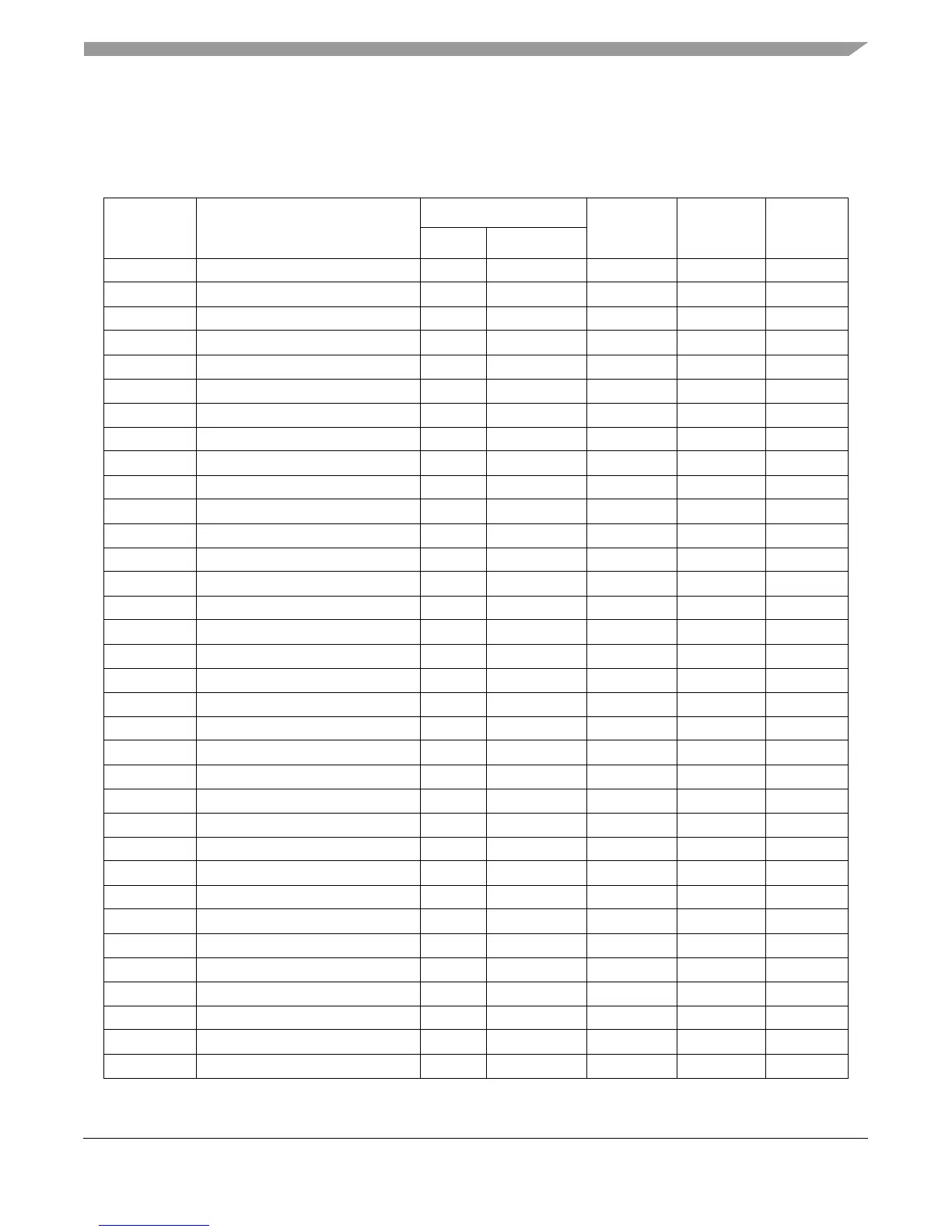

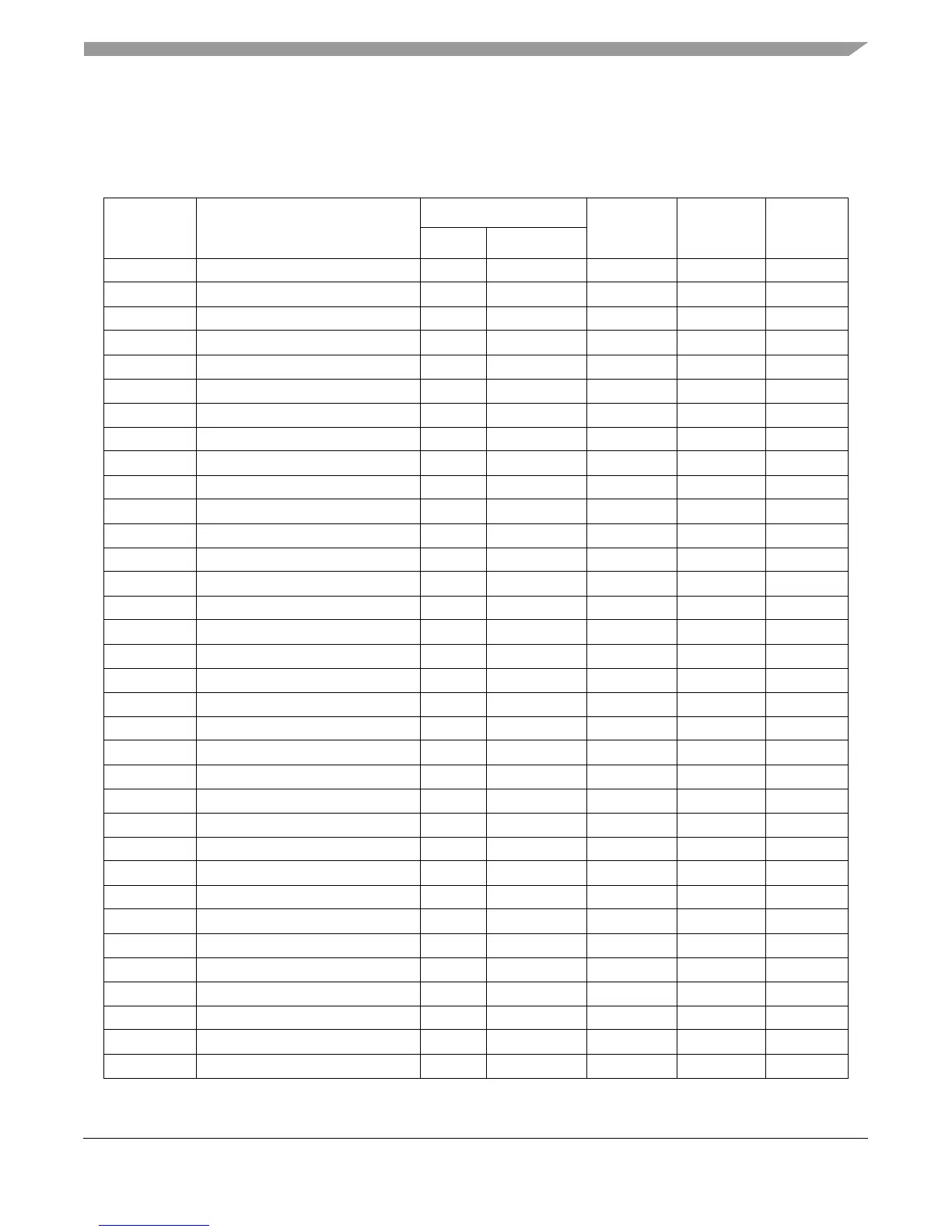

Table 3-23 summarizes all SPRs defined in Book E, indicating which are user-level access. The

SPR number column lists register numbers used in the instruction mnemonics.

Table 3-23. Book E Special-Purpose Registers (by SPR Abbreviation)

SPR

Abbreviation

Name

Defined SPR Number

Access

Supervisor

Only

Section/

Page

Decimal Binary

CSRR0 Critical save/restore register 0 58 00001 11010 Read/Write Yes 2.7.1.2/2-18

CSRR1 Critical save/restore register 1 59 00001 11011 Read/Write Yes 2.7.1.2/2-18

CTR Count register 9 00000 01001 Read/Write No 2.4.3/2-10

DAC1 Data address compare 1 316 01001 11100 Read/Write Yes 2.13.4/2-48

DAC2 Data address compare 2 317 01001 11101 Read/Write Yes 2.13.4/2-48

DBCR0 Debug control register 0 308 01001 10100 Read/Write Yes 2.13.1/2-46

DBCR1 Debug control register 1 309 01001 10101 Read/Write Yes 2.13.1/2-46

DBCR2 Debug control register 2 310 01001 10110 Read/Write Yes 2.13.1/2-46

DBSR Debug status register 304 01001 10000 Read/Clear

1

Ye s 2.13.2/2-47

DEAR Data exception address register 61 00001 11101 Read/Write Yes 2.7.1.3/2-18

DEC Decrementer 22 00000 10110 Read/Write Yes 2.6.4/2-16

DECAR Decrementer auto-reload 54 00001 10110 Write-only Yes 2.6.4/2-16

ESR Exception syndrome register 62 00001 11110 Read/Write Yes 2.7.1.6/2-20

IAC1 Instruction address compare 1 312 01001 11000 Read/Write Yes 2.13.3/2-48

IAC2 Instruction address compare 2 313 01001 11001 Read/Write Yes 2.13.3/2-48

IVOR0 Critical input 400 01100 10000 Read/Write Yes 2.7.1.5/2-19

IVOR1 Critical input interrupt offset 401 01100 10001 Read/Write Yes 2.7.1.5/2-19

IVOR2 Data storage interrupt offset 402 01100 10010 Read/Write Yes 2.7.1.5/2-19

IVOR3 Instruction storage interrupt offset 403 01100 10011 Read/Write Yes 2.7.1.5/2-19

IVOR4 External input interrupt offset 404 01100 10100 Read/Write Yes 2.7.1.5/2-19

IVOR5 Alignment interrupt offset 405 01100 10101 Read/Write Yes 2.7.1.5/2-19

IVOR6 Program interrupt offset 406 01100 10110 Read/Write Yes 2.7.1.5/2-19

IVOR8 System call interrupt offset 408 01100 11000 Read/Write Yes 2.7.1.5/2-19

IVOR10 Decrementer interrupt offset 410 01100 11010 Read/Write Yes 2.7.1.5/2-19

IVOR11 Fixed-interval timer interrupt offset 411 01100 11011 Read/Write Yes 2.7.1.5/2-19

IVOR12 Watchdog timer interrupt offset 412 01100 11100 Read/Write Yes 2.7.1.5/2-19

IVOR13 Data TLB error interrupt offset 413 01100 11101 Read/Write Yes 2.7.1.5/2-19

IVOR14 Instruction TLB error interrupt offset 414 01100 11110 Read/Write Yes 2.7.1.5/2-19

IVOR15 Debug interrupt offset 415 01100 11111 Read/Write Yes 2.7.1.5/2-19

IVPR Interrupt vector 63 00001 11111 Read/Write Yes 2.7.1.4/2-19

LR Link register 8 00000 01000 Read/Write No 2.4.2/2-10

PID Process ID register

2

48 00001 10000 Read/Write Yes 2.12.1/2-36

PIR Processor ID register 286 01000 11110 Read only Yes 2.5.2/2-12

PVR Processor version register 287 01000 11111 Read only Yes 2.5.3/2-13

Loading...

Loading...