PowerPC e500 Core Family Reference Manual, Rev. 1

3-28 Freescale Semiconductor

Instruction Model

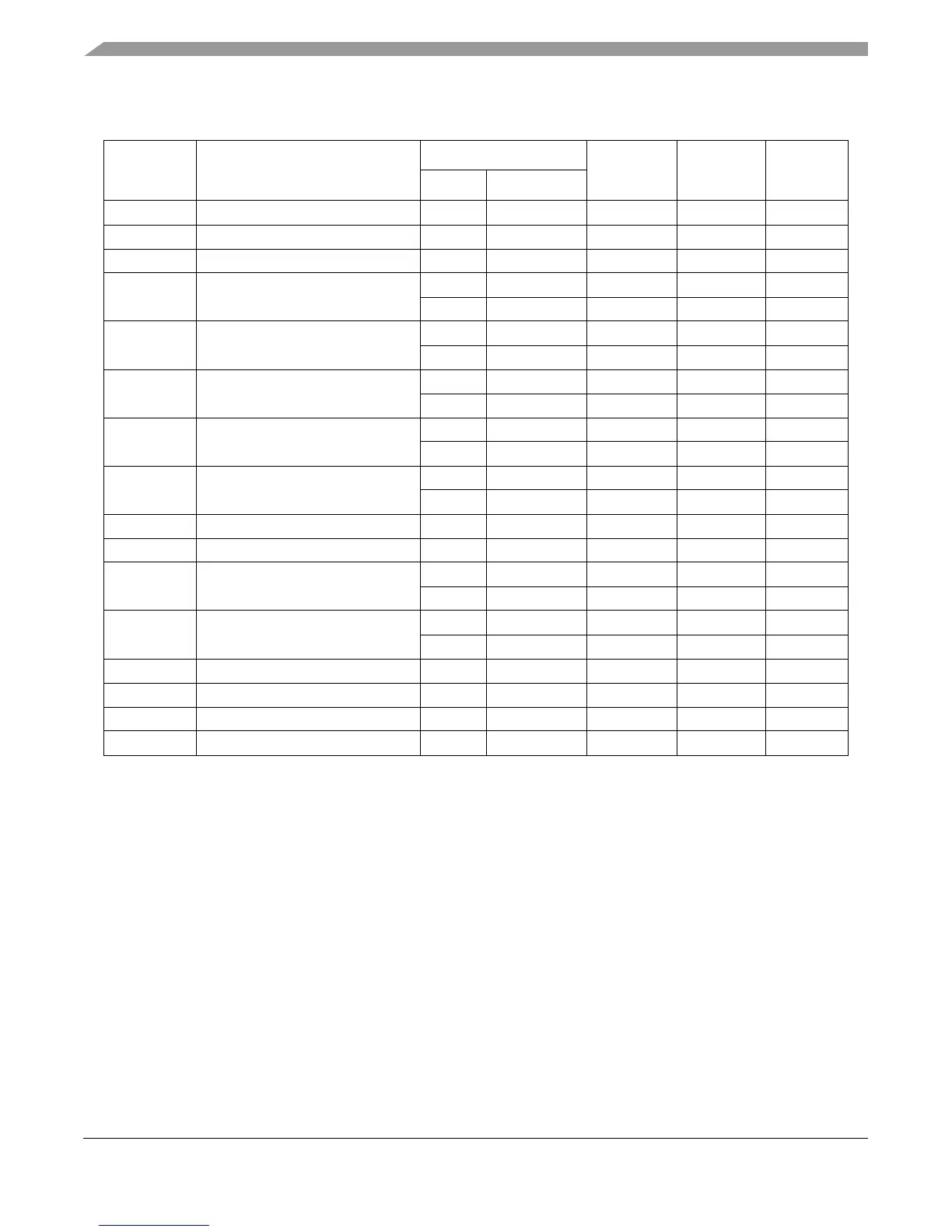

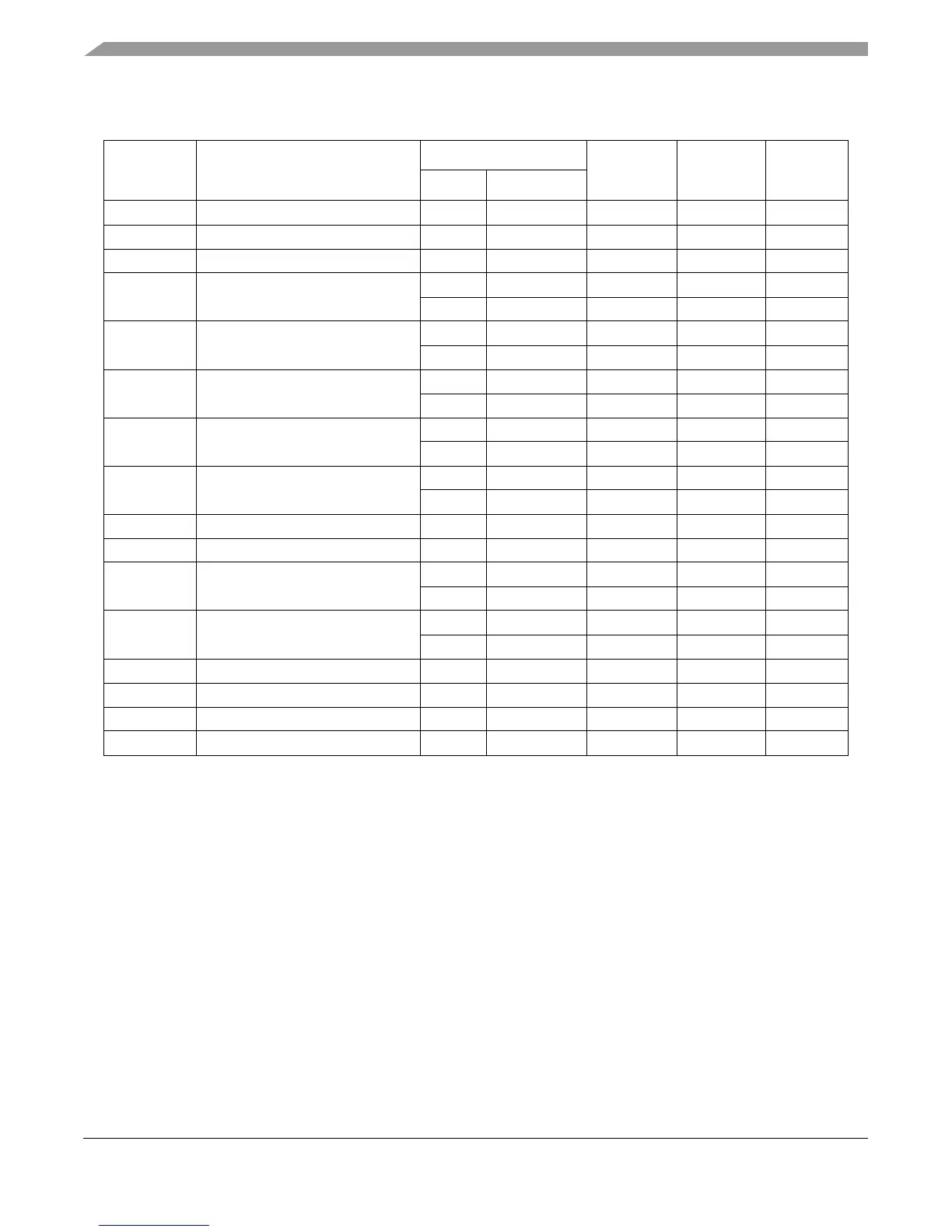

SPRG0 SPR general 0 272 01000 10000 Read/Write Yes 2.8/2-24

SPRG1 SPR general 1 273 01000 10001 Read/Write Yes 2.8/2-24

SPRG2 SPR general 2 274 01000 10010 Read/Write Yes 2.8/2-24

SPRG3 SPR general 3 259 01000 00011 Read only No

3

2.8/2-24

275 01000 10011 Read/Write Yes 2.8/2-24

SPRG4 SPR general 4 260 01000 00100 Read only No 2.8/2-24

276 01000 10100 Read/Write Yes 2.8/2-24

SPRG5 SPR general 5 261 01000 00101 Read only No 2.8/2-24

277 01000 10101 Read/Write Yes 2.8/2-24

SPRG6 SPR general 6 262 01000 00110 Read only No 2.8/2-24

278 01000 10110 Read/Write Yes 2.8/2-24

SPRG7 SPR general 7 263 01000 00111 Read only No 2.8/2-24

279 01000 10111 Read/Write Yes 2.8/2-24

SRR0 Save/restore register 0 26 00000 11010 Read/Write Yes 2.7.1.1/2-18

SRR1 Save/restore register 1 27 00000 11011 Read/Write Yes 2.7.1.1/2-18

TBL Time base lower 268 01000 01100 Read only No 2.6.3/2-16

284 01000 11100 Write-only Yes 2.6.3/2-16

TBU Time base upper 269 01000 01101 Read only No 2.6.3/2-16

285 01000 11101 Write-only Yes 2.6.3/2-16

TCR Timer control register 340 01010 10100 Read/Write Yes 2.6.1/2-15

TSR Timer status register 336 01010 10000 Read/Clear

4

Ye s 2.6.2/2-16

USPRG0 User SPR general 0

5

256 01000 00000 Read/Write No 2.8/2-24

XER Integer exception register 1 00000 00001 Read/Write No 2.3.2/2-9

1

The DBSR is read using mfspr. It cannot be directly written to. Instead, DBSR bits corresponding to 1 bits in the GPR

can be cleared using mtspr.

2

Implementations may support more than one PID. The e500 implements the Book E–defined PID as PID0.

3

User-mode read access to SPRG3 is implementation-dependent.

4

The TSR is read using mfspr. It cannot be directly written to. Instead, TSR bits corresponding to 1 bits in the GPR can

be cleared using mtspr.

5

USPRG0 is a separate physical register from SPRG0.

Table 3-23. Book E Special-Purpose Registers (by SPR Abbreviation) (continued)

SPR

Abbreviation

Name

Defined SPR Number

Access

Supervisor

Only

Section/

Page

Decimal Binary

Loading...

Loading...