PowerPC e500 Core Family Reference Manual, Rev. 1

5-6 Freescale Semiconductor

Interrupts and Exceptions

Table 5-3 shows ESR bit definitions.

Machine state register

(MSR)

MSR[38] is defined as the vector available bit (SPE). It functions as follows:

0 For the e500v2, if software attempts to execute an instruction that tries to access the upper word of

a 64-bit GPR, an SPE APU unavailable interrupt is taken. For the e500v1, the interrupt is also taken

if an attempt is made to execute an embedded SPFP scalar instruction.

1 Software can execute any embedded floating-point or SPE instructions.

EIS-Specific Interrupt Registers

Machine check

save/restore register 0

(MCSRR0)

When a machine check interrupt is taken, MCSRR0 is set to the current or next instruction address.

When rfmci is executed, instruction execution continues at the address in MCSRR0. In general,

MCSRR0 contains the address of the instruction that caused the machine check interrupt, or the

address of the instruction to return to after a machine check interrupt is serviced.

Machine check

save/restore register 1

(MCSRR1)

When a machine check interrupt is taken, MSR contents are placed into MCSRR1. When rfmci is

executed, MCSRR1 contents are restored to MSR. MCSRR1 bits that correspond to reserved MSR bits

are also reserved. Note that an MSR bit that is reserved may be altered by rfmci.

Machine check

syndrome register

(MCSR)

When a machine check interrupt is taken, the MCSR is updated to differentiate between machine check

conditions. Table 5-4 lists e500 bit assignments. The MCSR also indicates whether a machine check

condition is recoverable. ABIST status is logged in MCSR[48–54]. These read-only bits do not initiate

machine check (or any other interrupt). An ABIST bit being set indicates an error being detected in the

corresponding module.

Note that processors that do not implement the machine check APU use the Book E–defined ESR for

this purpose.

Machine check address

register (MCAR)

When a machine check interrupt is taken, MCAR is updated with the address of the data associated

with the machine check. Note that if a machine check interrupt is caused by a signal, the MCAR

contents are not meaningful. See Section 2.7.2.3, “Machine Check Address Register (MCAR).”

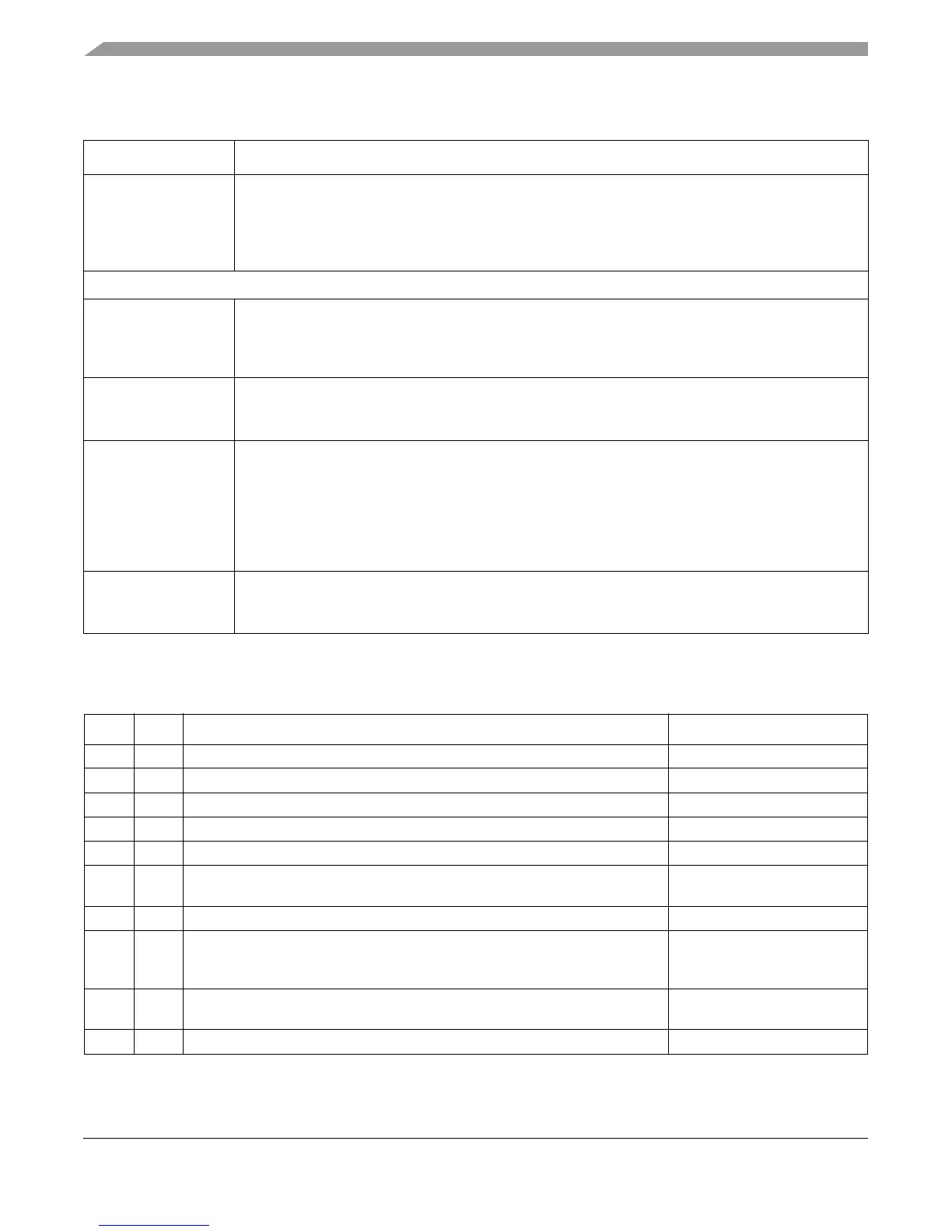

Table 5-3. Exception Syndrome Register (ESR) Definition

Bits Name Syndrome Interrupt Types

32–35 — Allocated —

36 PIL Illegal instruction exception Program

37 PPR Privileged instruction exception Program

38 PTR Trap exception Program

39 — Reserved, should be cleared. —

40 ST Store operation Alignment, data storage, data

TLB error

41 — Reserved, should be cleared. —

42 DLK Cache locking. Settings are implementation-dependent. On the e500, DLK is

set when a DSI occurs because dcbtls, dcbtstls, or dcblc is executed in user

mode and MSR[UCLE] = 0.

Data storage

43 ILK (EIS) Set when a DSI occurs because icbtl or icblc is executed in user mode

(MSR[PR] = 1) and MSR[UCLE] = 0

Data storage

44–45 — Reserved, should be cleared.

1

—

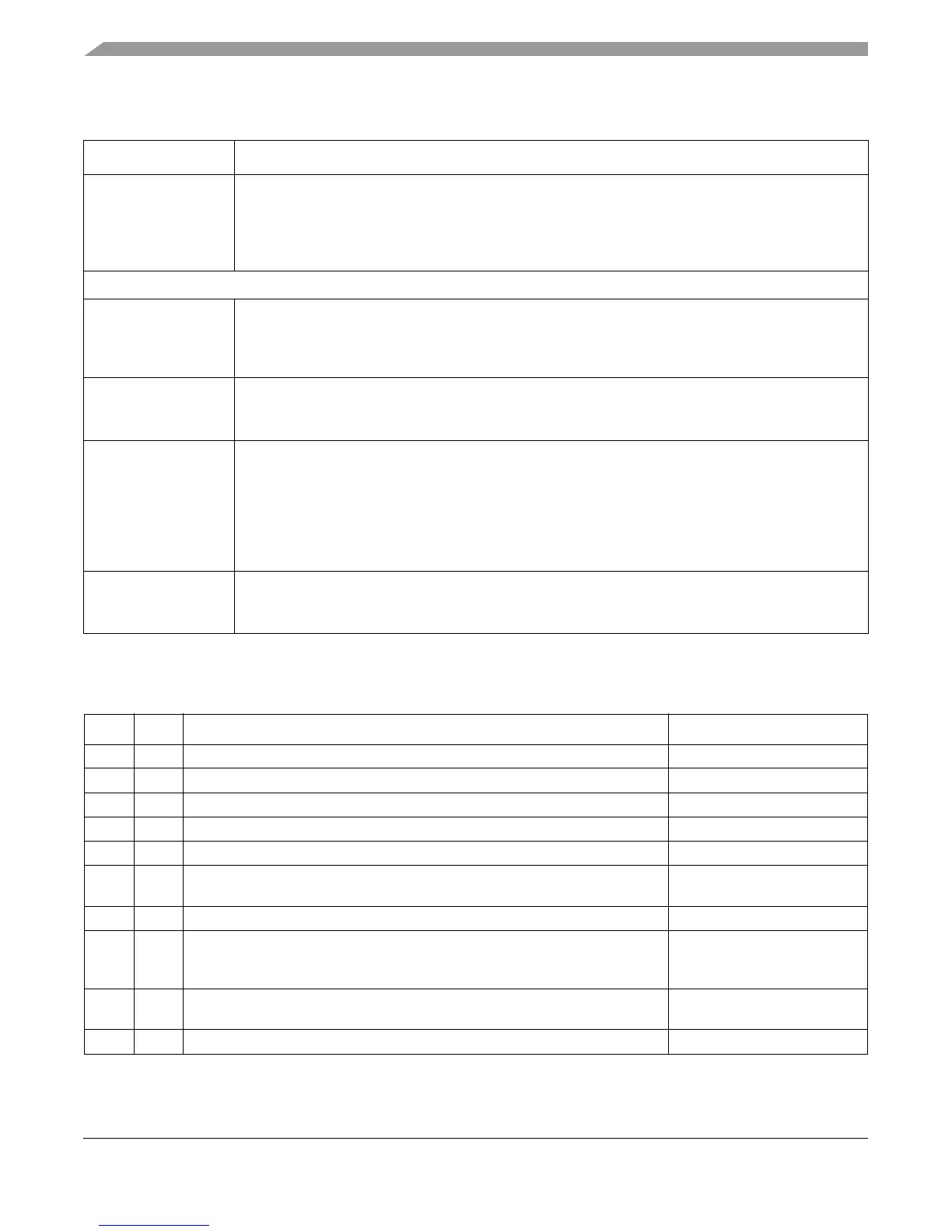

Table 5-2. Interrupt Registers Defined by the PowerPC Architecture (continued)

Register Description

Loading...

Loading...