Interrupts and Exceptions

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 5-7

An implementation may define additional ESR bits to identify implementation-specific or

architected interrupt types; the EIS defines ESR[ILK] and ESR[SPE].

NOTE

System software may need to identify the type of instruction that

caused the interrupt and examine the TLB entry and ESR to fully

identify the exception or exceptions. For example, because both

protection violation and byte-ordering exception conditions may be

present, and either causes a data storage interrupt, system software

would have to look beyond ESR[BO], such as the state of MSR[PR]

in SRR1 and the TLB entry page protection bits, to determine if a

protection violation also occurred.

Table 5-4 shows MCSR bit definitions. Section 5.7.2.1, “Core Complex Bus (CCB) and L1 Cache

Machine Check Errors,” provides information about machine check recoverability.

46 BO Byte-ordering exception Data storage, instruction

storage

47–55 — Reserved, should be cleared. —

56 SPE SPE exception bit. Book E allocates this bit for implementation-dependent use,

so it may have different functions on other implementations.

—

57–63 — Allocated for implementation-dependent use. Reserved, should be cleared. —

1

Book E defines bit 45 as PUO (unimplemented operation exception). On the e500, unimplemented instructions are handled

as illegal instructions.

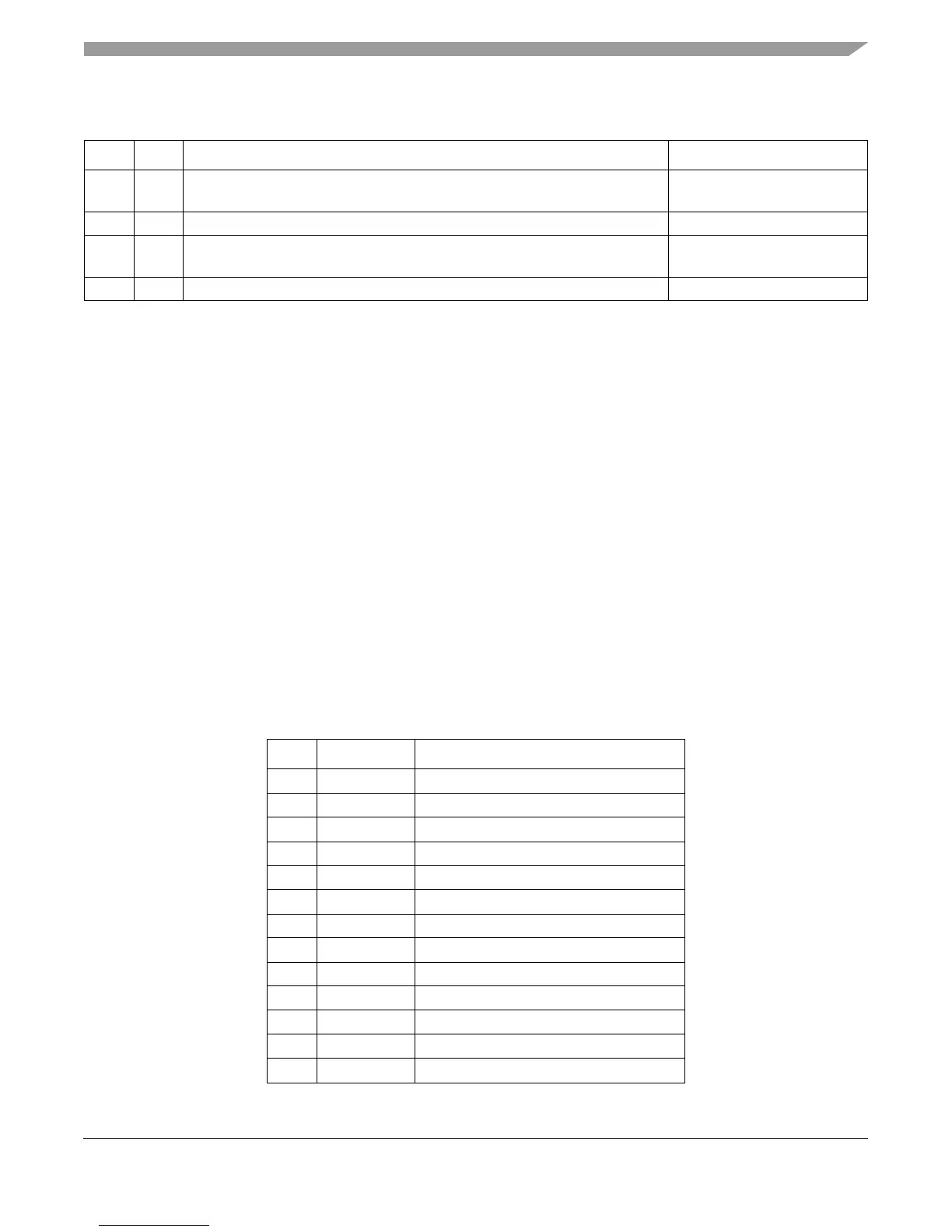

Table 5-4. Machine Check Syndrome Register (MCSR) Field Descriptions

Bits Name Description

32 MCP Machine check input signal

33 ICPERR Instruction cache parity error

34 DCP_PERR Data cache push parity error

35 DCPERR Data cache parity error

36–55 — Reserved, should be cleared.

56 BUS_IAERR Bus instruction address error

57 BUS_RAERR Bus read address error

58 BUS_WAERR Bus write address error

59 BUS_IBERR Bus instruction data bus error

60 BUS_RBERR Bus read data bus error

61 BUS_WBERR Bus write bus error

62 BUS_IPERR Bus instruction parity error

63 BUS_RPERR Bus read parity error

Table 5-3. Exception Syndrome Register (ESR) Definition (continued)

Bits Name Syndrome Interrupt Types

Loading...

Loading...