Performance Monitor

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 7-13

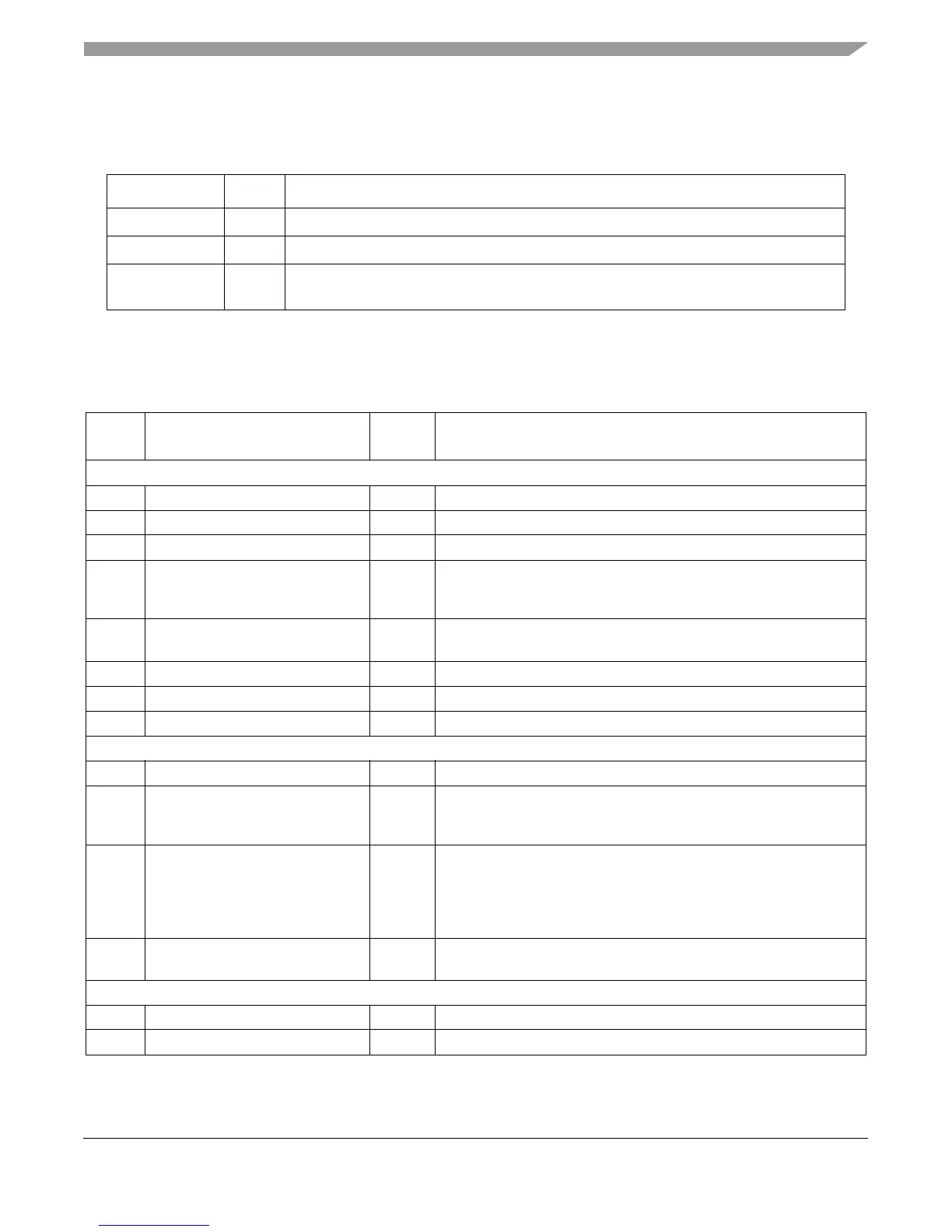

Table 7-9 describes how event types are indicated in Table 7-10.

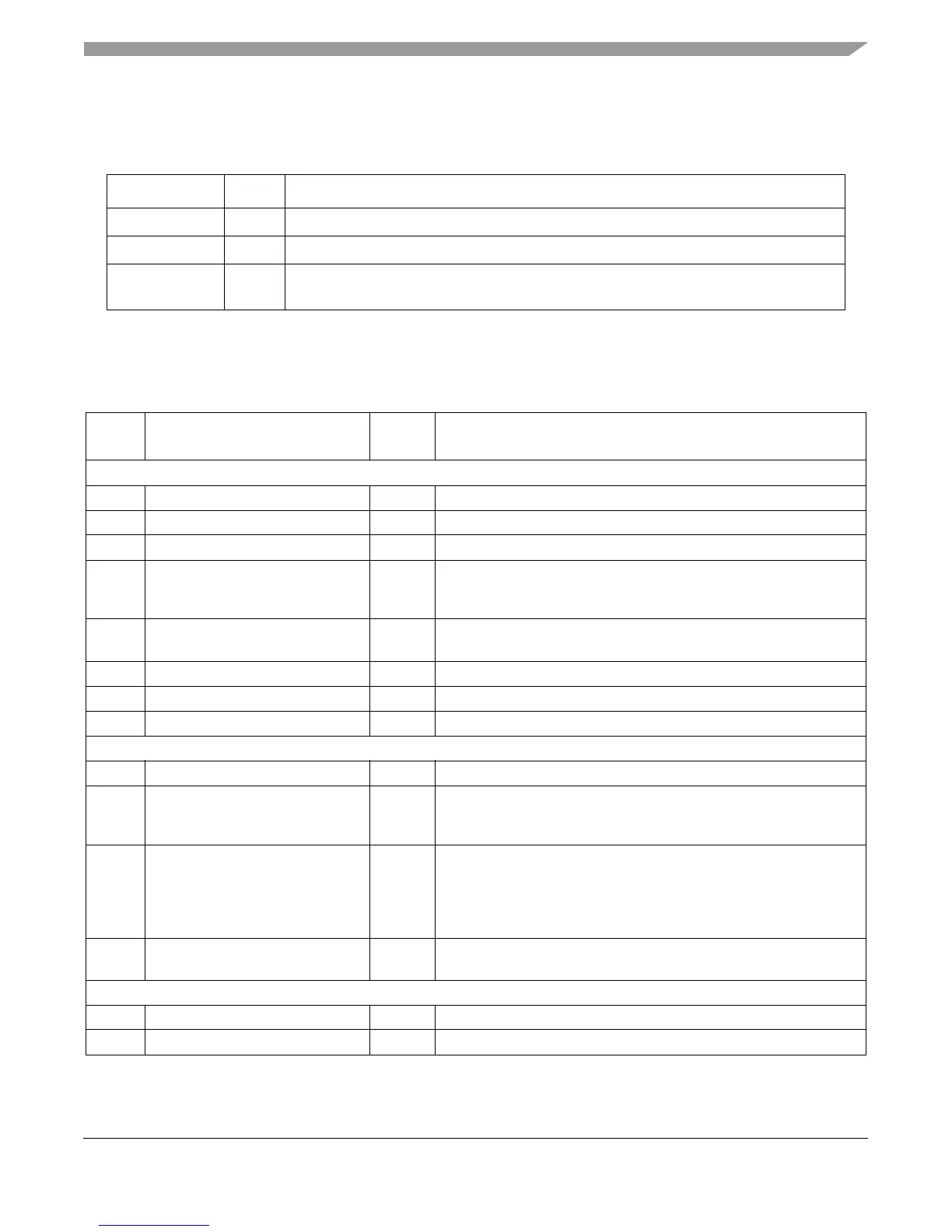

Table 7-10 describes performance monitor events. Pipeline events in Table 7-10 are defined in

Chapter 4, “Execution Timing.”

Table 7-9. Event Types

Event Type Label Description

Reference Ref:# Shared across counters PMC0—PMC3. Applicable to most microprocessors.

Common Com:# Shared across counters PMC0–PMC3. Fairly specific to e500 microarchitectures.

Counter-specific C[0–3]:# Counted only on one or more specific counters. The notation indicates the counter to which

an event is assigned. For example, an event assigned to counter PMC2 is shown as C2:#.

Table 7-10. Performance Monitor Event Selection

Number Event

Spec/

Nonspec

Count Description

General Events

Ref:0 Nothing Nonspec Register counter holds current value

Ref:1 Processor cycles Nonspec Every processor cycle

Ref:2 Instructions completed Nonspec Completed instructions. 0, 1, or 2 per cycle.

Com:3 Micro-ops completed

1

Nonspec Completed micro-ops. 0, 1, or 2 per cycle. (1 for each standard

instruction, 2 for load/store-with-update. 1–32 for load or store

multiple instructions)

Com:4 Instructions fetched Spec Fetched instructions. 0, 1, 2, 3, or 4 per cycle. (instructions written to

the IQ.)

Com:5 Micro-ops decoded

1

Spec Micro-ops decoded. 0, 1, or 2 per cycle. (2 for load/store-with-update)

Com:6 PM_EVENT transitions Spec 0 to 1 transitions on the

pm_event

input.

Com:7 PM_EVENT cycles Spec Processor cycles that occur when the

pm_event

input is asserted.

Instruction Types Completed

Com:8 Branch instructions completed Nonspec Completed branch instructions.

Com:9 Load micro-ops completed

1

Nonspec Completed load micro-ops. (l*, evl*, load-update (1 load micro-op),

load-multiple (1–32 micro-ops), dcbt(L1, CT = 0), and dcbtst(L1, CT

= 0)

Com:10 Store micro-ops completed

1

Nonspec Completed store micro-ops. (st*, evst*, store-update (1 store

micro-op), store-multiple (1–32 micro-ops), tlbivax, icbi, icblc,

icbtls, dcba, dcbf, dcblc, dcbst, dcbt(L2, CT = 1), dcbtls,

dcbtst(L2, CT = 1), dcbtstls, dcbz, icbt(L2, CT = 1), mbar, and

msync)

Com:11 Number of CQ redirects Nonspec Fetch redirects initiated from the completion unit. (for example,

resulting from sc, rfi, rfci, rfmci, isync, and interrupts)

Branch Prediction and Execution Events

Com:12 Branches finished Spec Includes all branch instructions

Com:13 Taken branches finished Spec Includes all taken branch instructions

Loading...

Loading...