PowerPC e500 Core Family Reference Manual, Rev. 1

7-14 Freescale Semiconductor

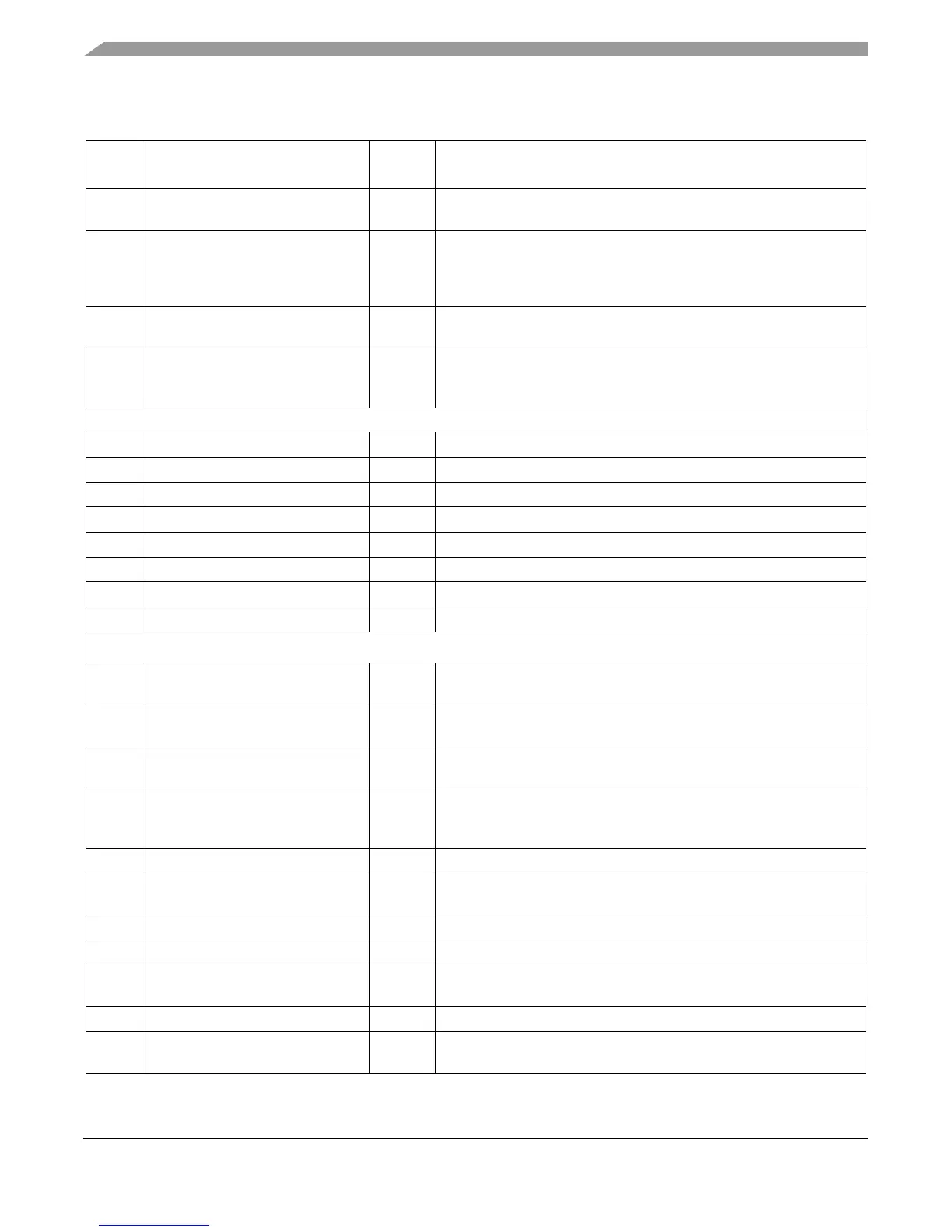

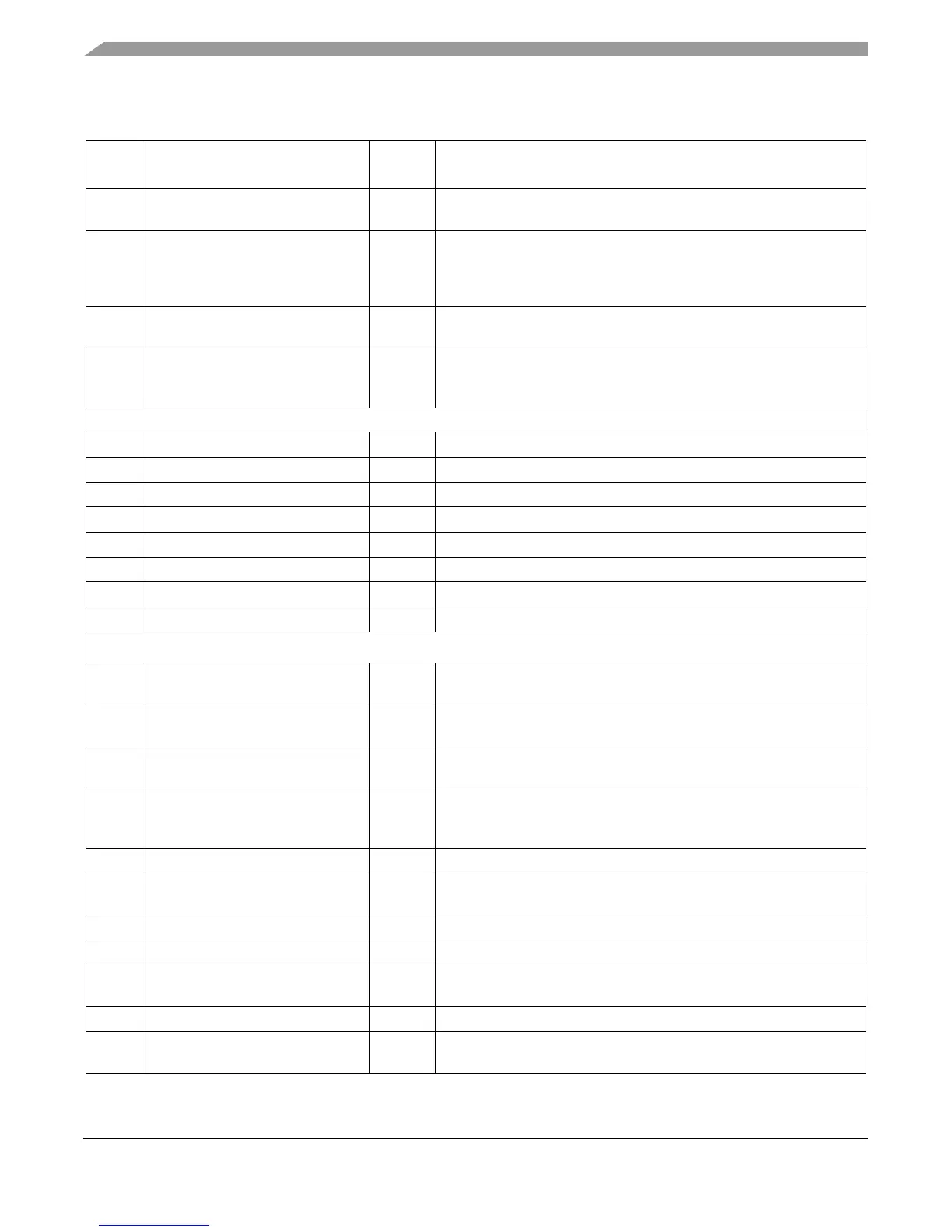

Performance Monitor

Com:14 Finished unconditional branches

that miss the BTB

Spec Includes all taken branch instructions not allocated in the BTB

Com:15 Branches mispredicted (for any

reason)

Spec Counts branch instructions mispredicted due to direction, target (for

example if the CTR contents change), or IAB prediction. Does not

count instructions that the branch predictor incorrectly predicted to

be branches.

Com:16 Branches in the BTB mispredicted

due to direction prediction.

Spec Counts branch instructions mispredicted due to direction prediction.

Com:17 BTB hits and pseudo-hits Spec Branch instructions that hit in the BTB or miss in the BTB and are

not-taken (a pseudo-hit). Characterizes upper bound on prediction

rate.

Pipeline Stalls

Com:18 Cycles decode stalled Spec Cycles the IQ is not empty but 0 instructions decoded

Com:19 Cycles issue stalled Spec Cycles the issue buffer is not empty but 0 instructions issued

Com:20 Cycles branch issue stalled Spec Cycles the branch buffer is not empty but 0 instructions issued

Com:21 Cycles SU1 schedule stalled Spec Cycles SU1 is not empty but 0 instructions scheduled

Com:22 Cycles SU2 schedule stalled Spec Cycles SU2 is not empty but 0 instructions scheduled

Com:23 Cycles MU schedule stalled Spec Cycles MU is not empty but 0 instructions scheduled

Com:24 Cycles LRU schedule stalled Spec Cycles LRU is not empty but 0 instructions scheduled

Com:25 Cycles BU schedule stalled Spec Cycles BU is not empty but 0 instructions scheduled

Load/Store, Data Cache, and Data Line Fill Buffer (DLFB) Events

Com:26 Total translated Spec Total of load and store micro-ops that reach the second stage of the

LSU

1, 2

Com:27 Loads translated Spec Cacheable l* or evl* micro-ops translated. (includes load micro-ops

from load-multiple and load-update instructions)

1,2

Com:28 Stores translated Spec Cacheable st* or evst* micro-ops translated. (includes micro-ops

from store-multiple, and store-update instructions)

1,2

Com:29 Touches translated Spec Cacheable dcbt and dcbtst instructions translated (L1 only) (Doesn’t

count touches that are converted to nops i.e. exceptions,

noncacheable, HID0[NOPTI] is set.)

Com:30 Cacheops translated Spec dcba, dcbf, dcbst, and dcbz instructions translated.

Com:31 Cache-inhibited accesses

translated

Spec Cache inhibited accesses translated

Com:32 Guarded loads translated Spec Guarded loads translated

Com:33 Write-through stores translated Spec Write-through stores translated

Com:34 Misaligned load or store accesses

translated

Spec Misaligned load or store accesses translated.

Com:35 Total allocated to DLFB Spec —

Com:36 Loads translated and allocated to

DLFB

Spec Applies to same class of instructions as loads translated.

Table 7-10. Performance Monitor Event Selection (continued)

Number Event

Spec/

Nonspec

Count Description

Loading...

Loading...