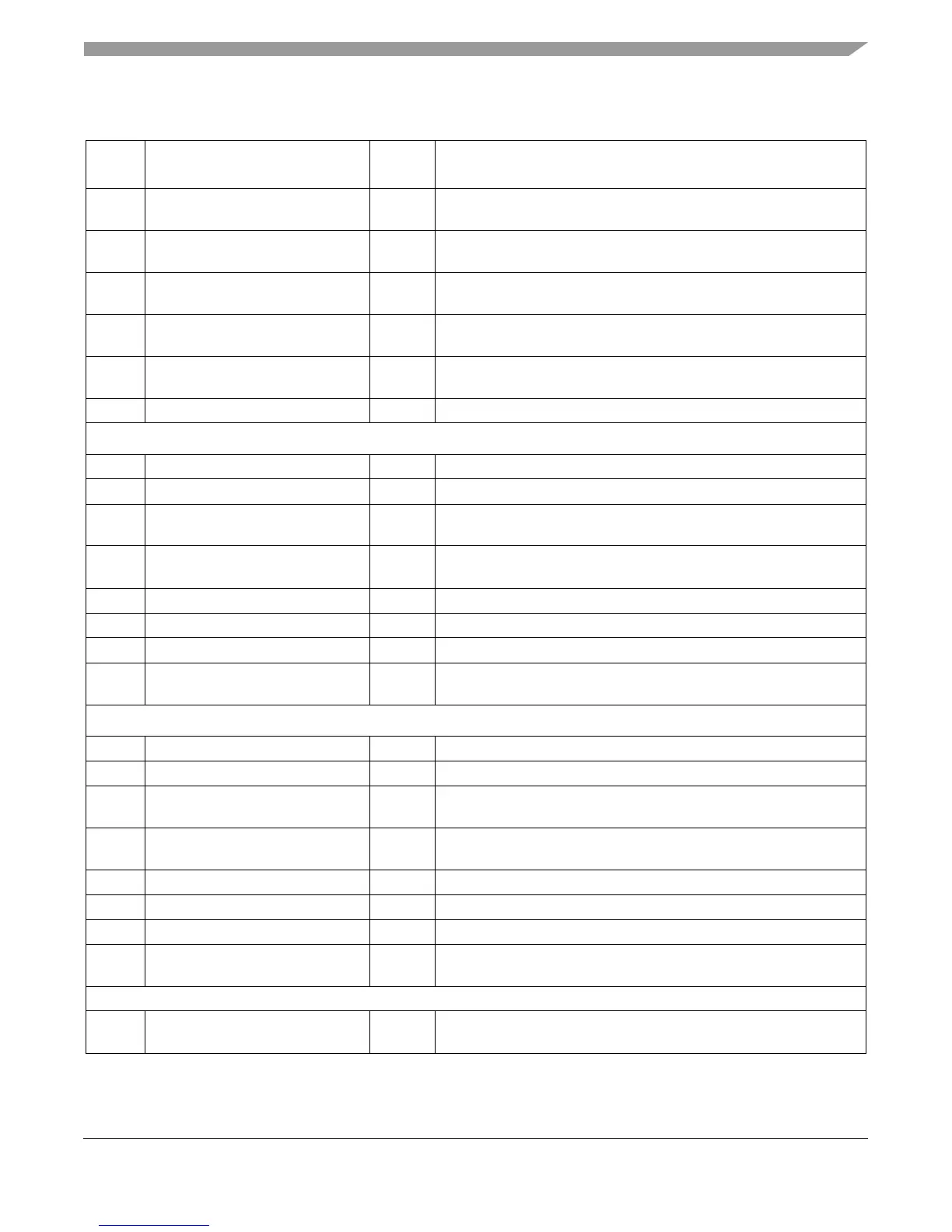

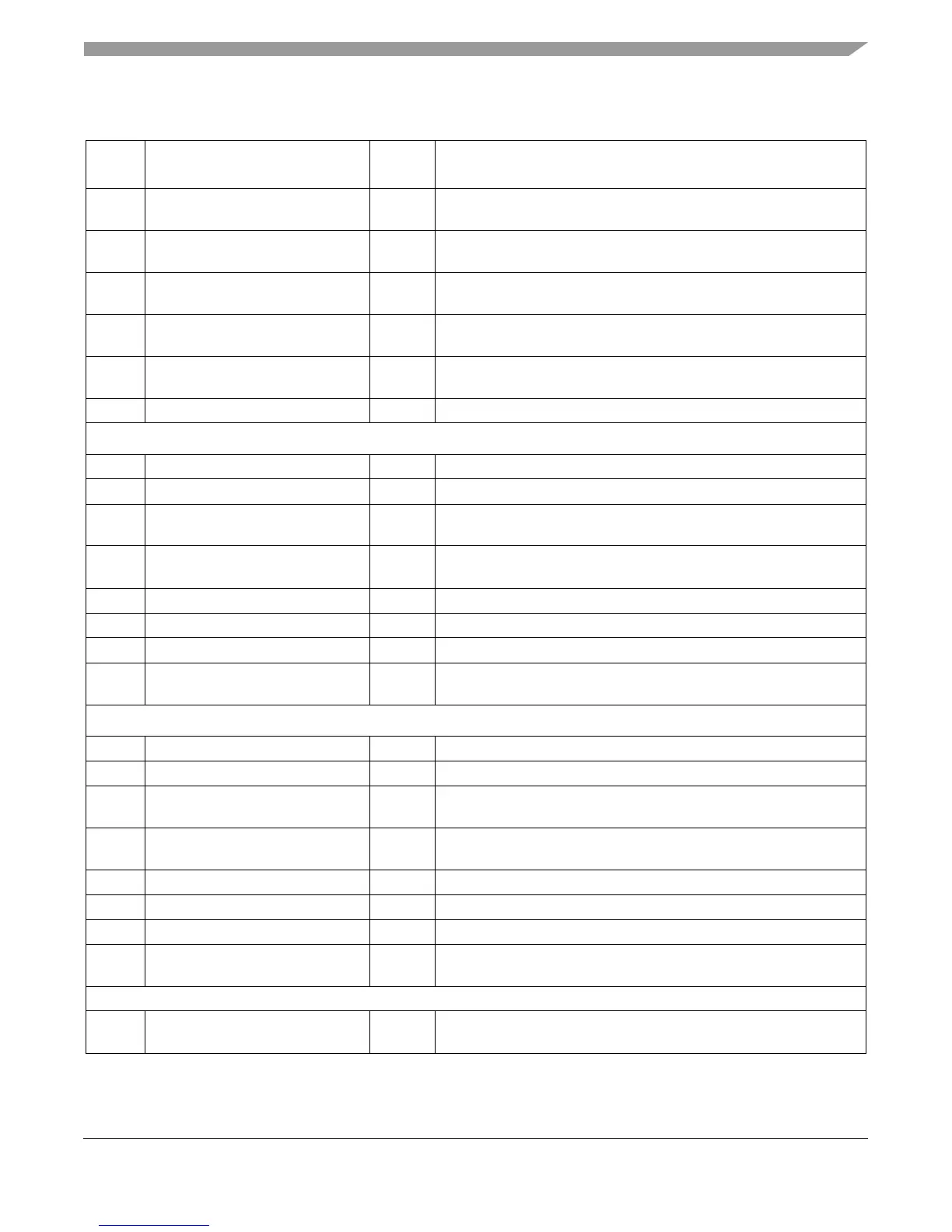

Performance Monitor

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 7-15

Com:37 Stores completed and allocated to

DLFB

Nonspec Applies to same class of instructions as stores translated.

Com:38 Touches translated and allocated to

DLFB

Spec Applies to same class of instructions as touches translated.

Com:39 Stores completed Nonspec Cacheable st* or evst* micro-ops completed. (Applies to the same

class of instructions as stores translated.)

1,2

Com:40 Data L1 cache locks Nonspec Cache lines locked in the data L1 cache. (Counts a lock even if an

overlock condition occurs.)

Com:41 Data L1 cache reloads Spec Counts cache reloads for any reason. Typically used to determine

data cache miss rate (along with loads/stores completed).

Com:42 Data L1 cache castouts Spec Does not count castouts due to dcbf.

Data Side Replay Conditions: Times Detected

Com:43 Load miss with DLFB full. Spec Counts number of stalls; Com:51 counts cycles stalled.

Com:44 Load miss with load queue full. Spec Counts number of stalls; Com:52 counts cycles stalled.

Com:45 Load guarded miss when the load is

not yet at the bottom of the CQ.

Spec Counts number of stalls; Com:53 counts cycles stalled.

Com:46 Translate a store when the store

queue is full.

Spec Counts number of stalls; Com:54 counts cycles stalled.

Com:47 Address collision. Spec Counts number of stalls; Com:55 counts cycles stalled.

Com:48 Data MMU miss. Spec Counts number of stalls; Com:56 counts cycles stalled.

Com:49 Data MMU busy. Spec Counts number of stalls; Com:57 counts cycles stalled.

Com:50 Second part of misaligned access

when first part missed in cache.

Spec Counts number of stalls; Com:58 counts cycles stalled.

Data Side Replay Conditions: Cycles Stalled

Com:51 Load miss with DLFB full. Spec Counts cycles stalled; Com:43 counts number of stalls.

Com:52 Load miss with load queue full. Spec Counts cycles stalled; Com:44 counts number of stalls.

Com:53 Load guarded miss when the load is

not yet at the bottom of the CQ.

Spec Counts cycles stalled; Com:45 counts number of stalls.

Com:54 Translate a store when the store

queue is full.

Spec Counts cycles stalled; Com:46 counts number of stalls.

Com:55 Address collision. Spec Counts cycles stalled; Com:47 counts number of stalls.

Com:56 Data MMU miss. Spec Counts cycles stalled; Com:48 counts number of stalls.

Com:57 Data MMU busy. Spec Counts cycles stalled; Com:49 counts number of stalls.

Com:58 Second part of misaligned access

when first part missed in cache.

Spec Counts cycles stalled; Com:50 counts number of stalls.

Fetch, Instruction Cache, Instruction Line Fill Buffer (ILFB), and Instruction Prefetch Events

Com:59 Instruction L1 cache locks Nonspec Counts cache lines locked in the instruction L1 cache. (Counts a lock

even if an overlock occurs.)

Table 7-10. Performance Monitor Event Selection (continued)

Number Event

Spec/

Nonspec

Count Description

Loading...

Loading...