PowerPC e500 Core Family Reference Manual, Rev. 1

7-16 Freescale Semiconductor

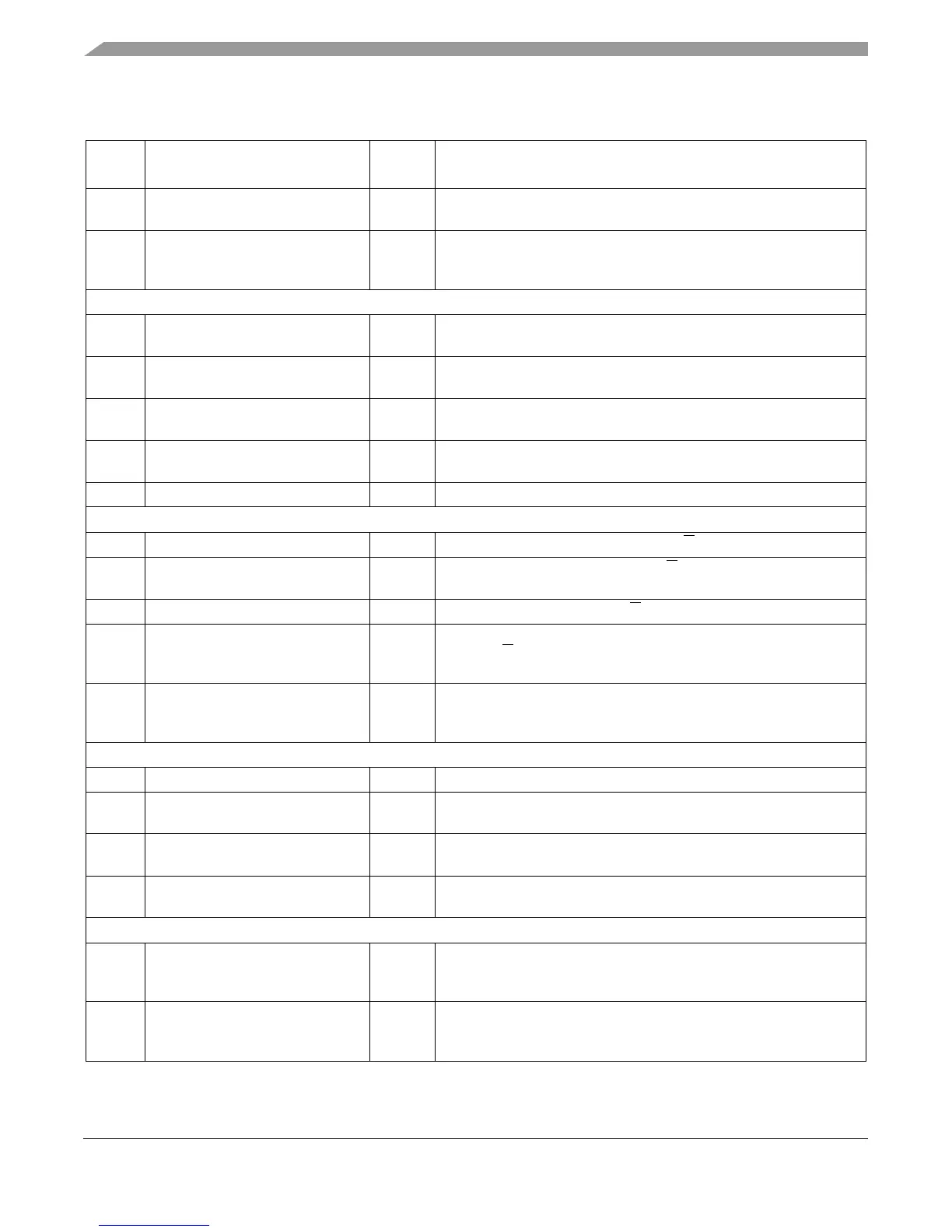

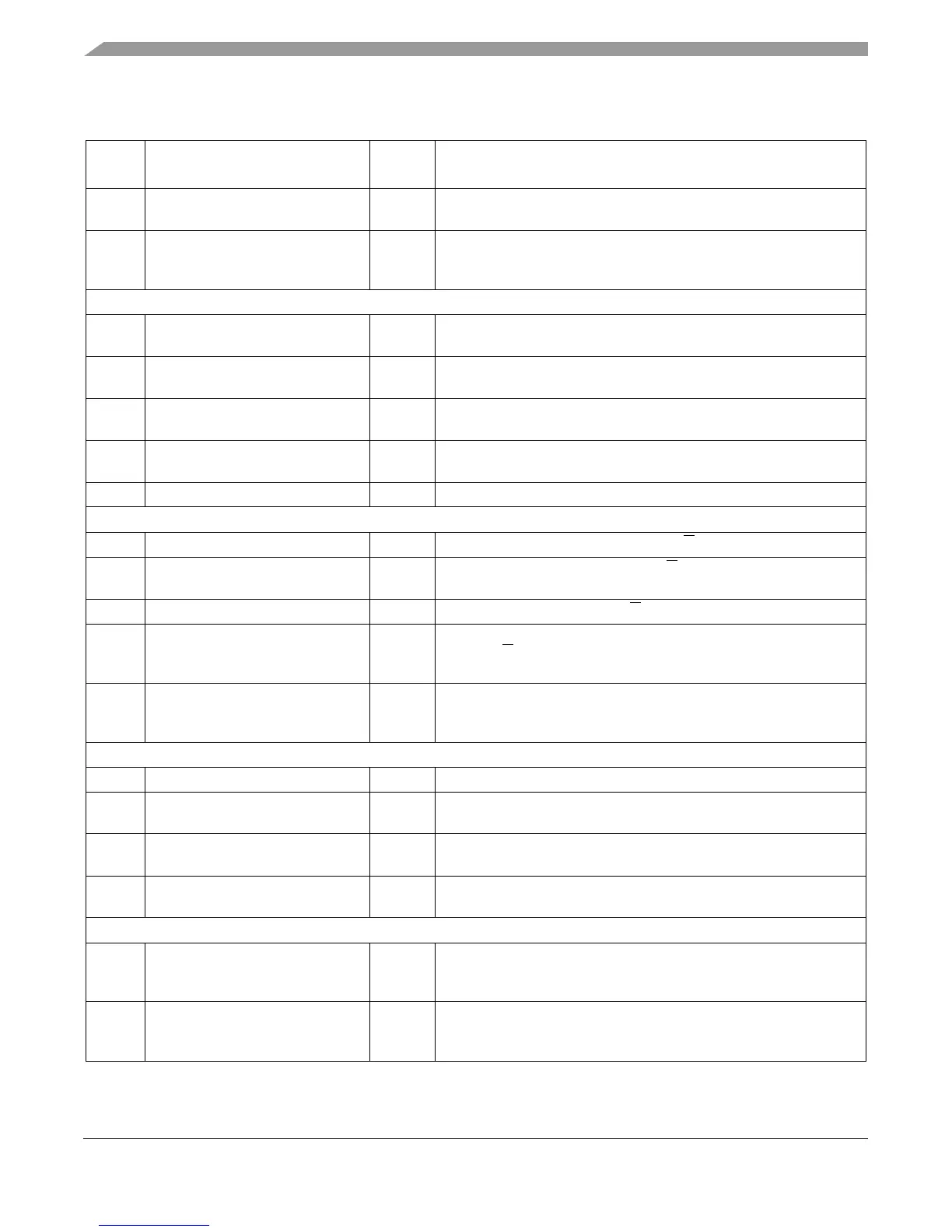

Performance Monitor

Com:60 Instruction L1 cache reloads from

fetch

Spec Counts reloads due to demand fetch. Typically used to determine

instruction cache miss rate (along with instructions completed)

Com:61 Number of fetches Spec Counts fetches that write at least one instruction to the IQ. (With

instruction fetched (com:4), can used to compute

instructions-per-fetch)

Instruction MMU, Data MMU and L2 MMU Events

Com:62 Instruction MMU TLB4K reloads Spec Counts reloads in the level 1 instruction MMU TLB4K.þA reload in the

level 2 MMU TLB4Kis not counted.

Com:63 Instruction MMU VSP reloads Spec Counts reloads in the level 1 instruction MMU VSP.þA reload in the

level 2 MMU VSP is not counted.

Com:64 Data MMU TLB4K reloads Spec Counts reloads in the level 1 data MMU TLB4K.þA reload in the level

2 MMU TLB4K is not counted.

Com:65 Data MMU VSP reloads Spec Counts reloads in the level 1 data MMU VSP.þA reload in the level 2

MMU VSP is not counted.

Com:66 L2MMU misses Nonspec Counts instruction TLB/data TLB error interrupts

BIU Interface Usage

Com:67 BIU master requests Spec Master transaction starts (assertions of

ts

Com:68 BIU master instruction-side

requests

Spec Master instruction-side assertions of

ts

Com:69 BIU master data-side requests Spec Master data-side assertions of

ts

Com:70 BIU master data-side castout

requests

Spec Includes replacement pushes and snoop pushes, but not DCBF

castouts. (

ts

assertions caused by master data-side

non-program-demand castouts)

Com:71 BIU master retries Spec Transactions initiated by this processor that were retried on the BIU

interface. (The e500 is master and another device retries the e500

transaction.)

Snoop

Com:72 Snoop requests N/A Externally generated snoop requests. (Counts snoop TSs.)

Com:73 Snoop hits N/A Snoop hits on all data-side resources regardless of the cache state

(modified or exclusive)

Com:74 Snoop pushes N/A Snoop pushes from all data-side resources. (Counts snoop ARTRYs

and WOPs.)

Com:75 Snoop retries N/A Retried snoop requests. (Counts snoop ARTRYs.) (opposite of com

71—another device drives

artry

).

Threshold Events

C0:76

C1:76

Data line fill buffer load miss cycles Spec Instances when the number of cycles between a load allocation in the

data line fill buffer (entry 0) and write-back to the data L1 cache

exceeds the threshold.

C0:77

C1:77

ILFB fetch miss cycles Spec Instances when the number of cycles between allocation in the ILFB

(entry 0) and write-back to the instruction L1 cache exceeds the

threshold.

Table 7-10. Performance Monitor Event Selection (continued)

Number Event

Spec/

Nonspec

Count Description

Loading...

Loading...