Performance Monitor

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 7-17

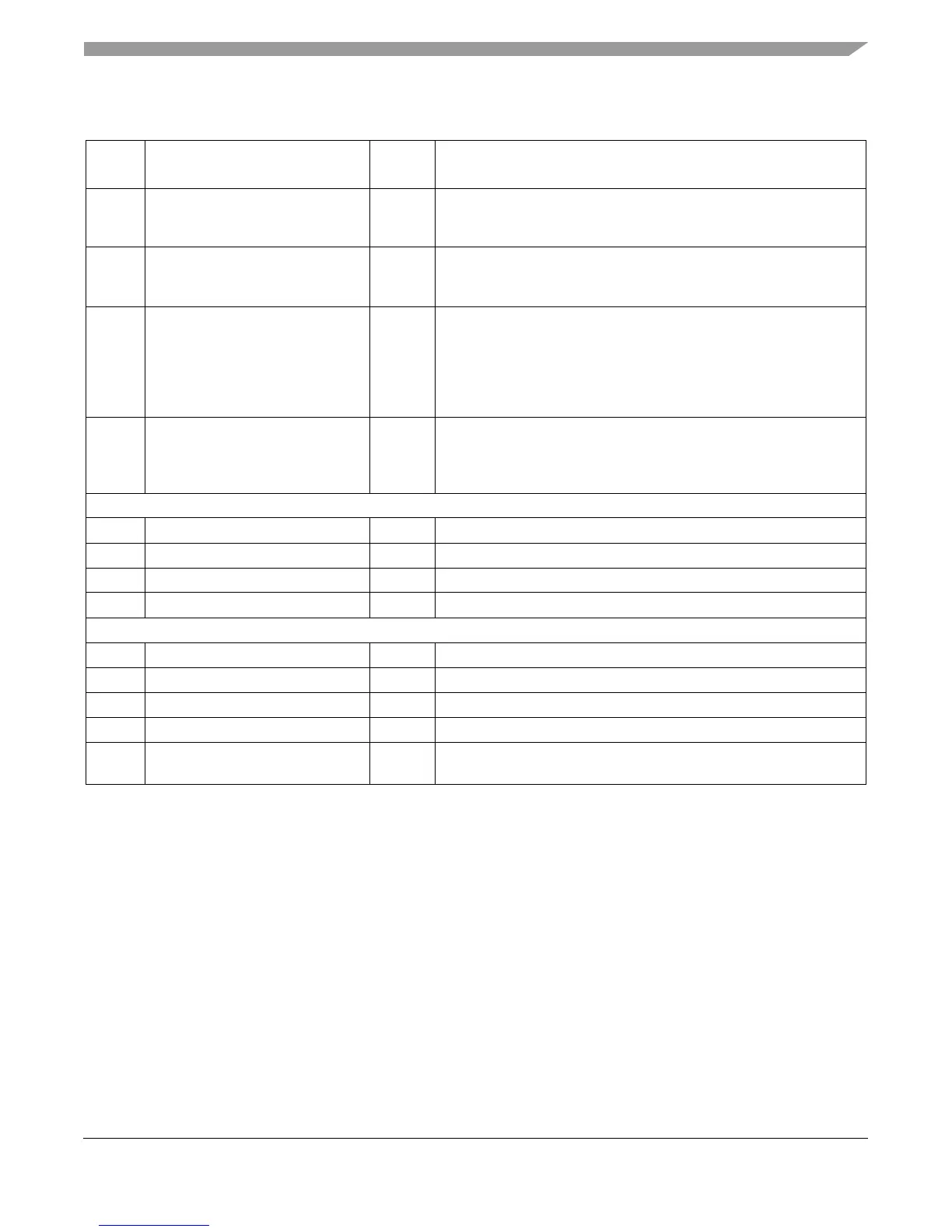

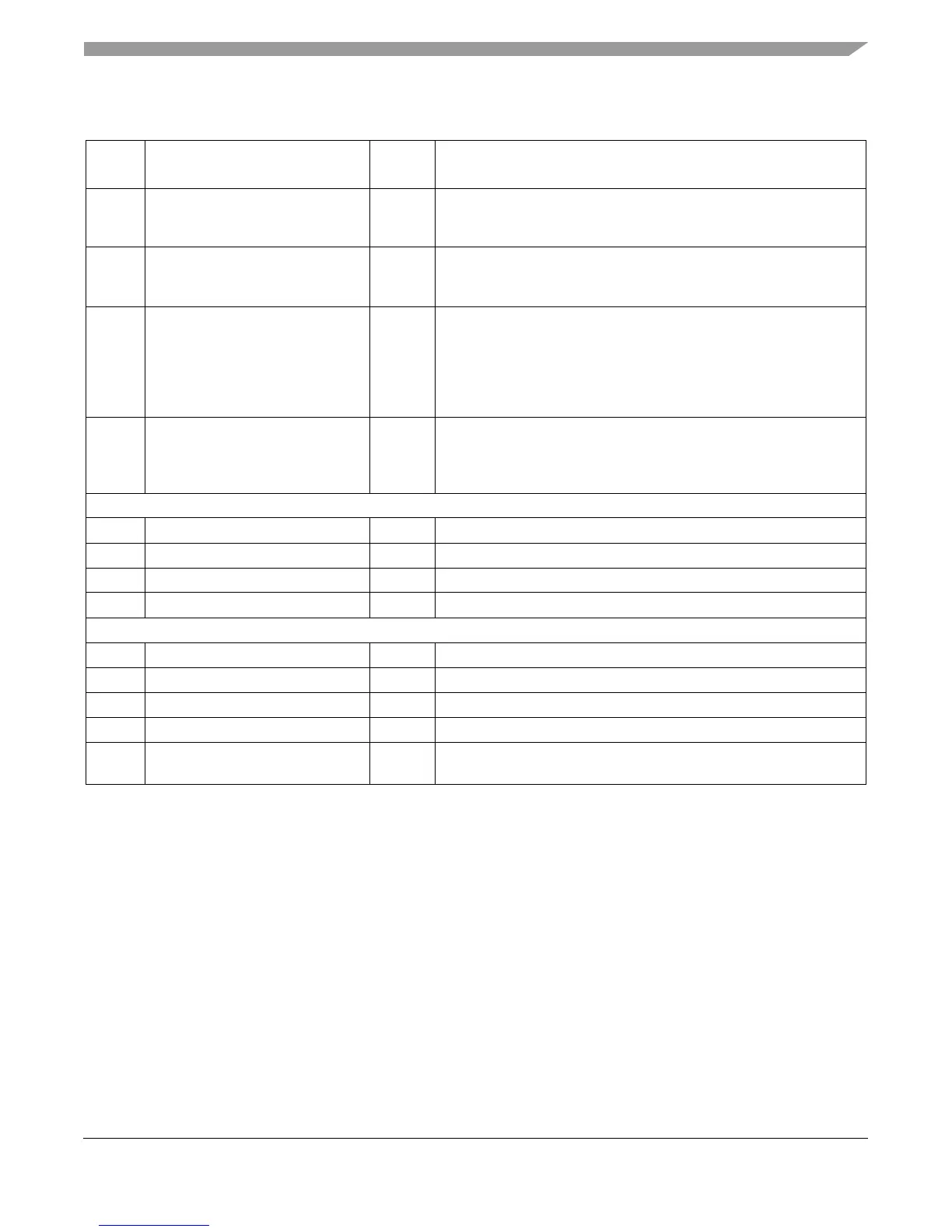

C0:78

C1:78

External input interrupt latency

cycles

N/A Instances when the number of cycles between request for interrupt

(

int

) asserted (but possibly masked/disabled) and redirecting fetch to

external interrupt vector exceeds threshold.

C0:79

C1:79

Critical input interrupt latency

cycles

N/A Instances when the number of cycles between request for critical

interrupt (

cint

) is asserted (but possibly masked/disabled) and

redirecting fetch to the critical interrupt vector exceeds threshold.

C0:80

C1:80

External input interrupt pending

latency cycles

N/A Instances when the number of cycles between external interrupt

pending (enabled and pin asserted) and redirecting fetch to the

external interrupt vector exceeds the threshold. Note that this and the

next event may count multiple times for a single interrupt if the

threshold is very small and the interrupt is masked a few cycles after

it is asserted and later becomes unmasked.

C0:81

C1:81

Critical input interrupt pending

latency cycles

N/A Instances when the number of cycles between pin request for critical

interrupt pending (enabled and pin asserted) and redirecting fetch to

the critical interrupt vector exceeds the threshold. See note for

previous event.

Chaining Events

3

Com:82 PMC0 overflow N/A PMC0[32] transitions from 1 to 0.

Com:83 PMC1 overflow N/A PMC1[32] transitions from 1 to 0.

Com:84 PMC2 overflow N/A PMC2[32] transitions from 1 to 0.

Com:85 PMC3 overflow N/A PMC3[32] transitioned from 1 to 0.

Interrupt Events

Com:86 Interrupts taken Nonspec —

Com:87 External input interrupts taken Nonspec —

Com:88 Critical input interrupts taken Nonspec —

Com:89 System call and trap interrupts Nonspec —

Ref:90 (e500v2 only) Transitions of TBL bit

selected by PMGC0[TBSEL].

Nonspec Counts transitions of the TBL bit selected by PMGC0[TBSEL].

1

Basic instructions are counted as one micro-op; load and store with update instructions count as one load or store micro-op

and one add micro-op; and load or store multiple instructions are counted as from 1–32 load or store micro-ops, depending

on how the instruction is encoded.

2

For load/store events, a micro-op is described as translated when the micro-op has successfully translated and is in the

second stage of the load/store translate pipeline.

3

For chaining events, if a counter is configured to count its own overflow bit, that counter does not increment. For example, if

PMC2 is selected to count PMC2 overflow events, PMC2 does not increment.

Table 7-10. Performance Monitor Event Selection (continued)

Number Event

Spec/

Nonspec

Count Description

Loading...

Loading...