Auxiliary Processing Units (APUs)

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 10-17

efdnabs efdnabs

Floating-Point Double-Precision Negative Absolute Value

efdnabs rD,rA

rD

0:63

← 0b1 || rA

1:63

The sign bit of rA is set to 1 and the result is placed into rD.

Exception detection for efdnabs is implementation dependent. On the e500v2, the exception is

handled as follows: If rA is Infinity, Denorm, or NaN, SPEFSCR[FINV] is set, and FG and FX are

cleared. If SPEFSCR[FINVE] = 0, the results are the same as for a normalized number. If

SPEFSCR[FINVE] = 1, an interrupt is taken and rD is not updated.

efdneg efdneg

Floating-Point Double-Precision Negate

efdneg rD,rA

rD

0:63

← ¬rA

0

|| rA

1:63

The sign bit of rA is complemented and the result is placed into rD.

Exception detection for efdneg is implementation dependent. On the e500v2, the exception is

handled as follows: If rA is Infinity, Denorm, or NaN, SPEFSCR[FINV] is set, and FG and FX are

cleared. If SPEFSCR[FINVE] = 0, the results are the same as for a normalized number. If

SPEFSCR[FINVE] = 1, an interrupt is taken and rD is not updated.

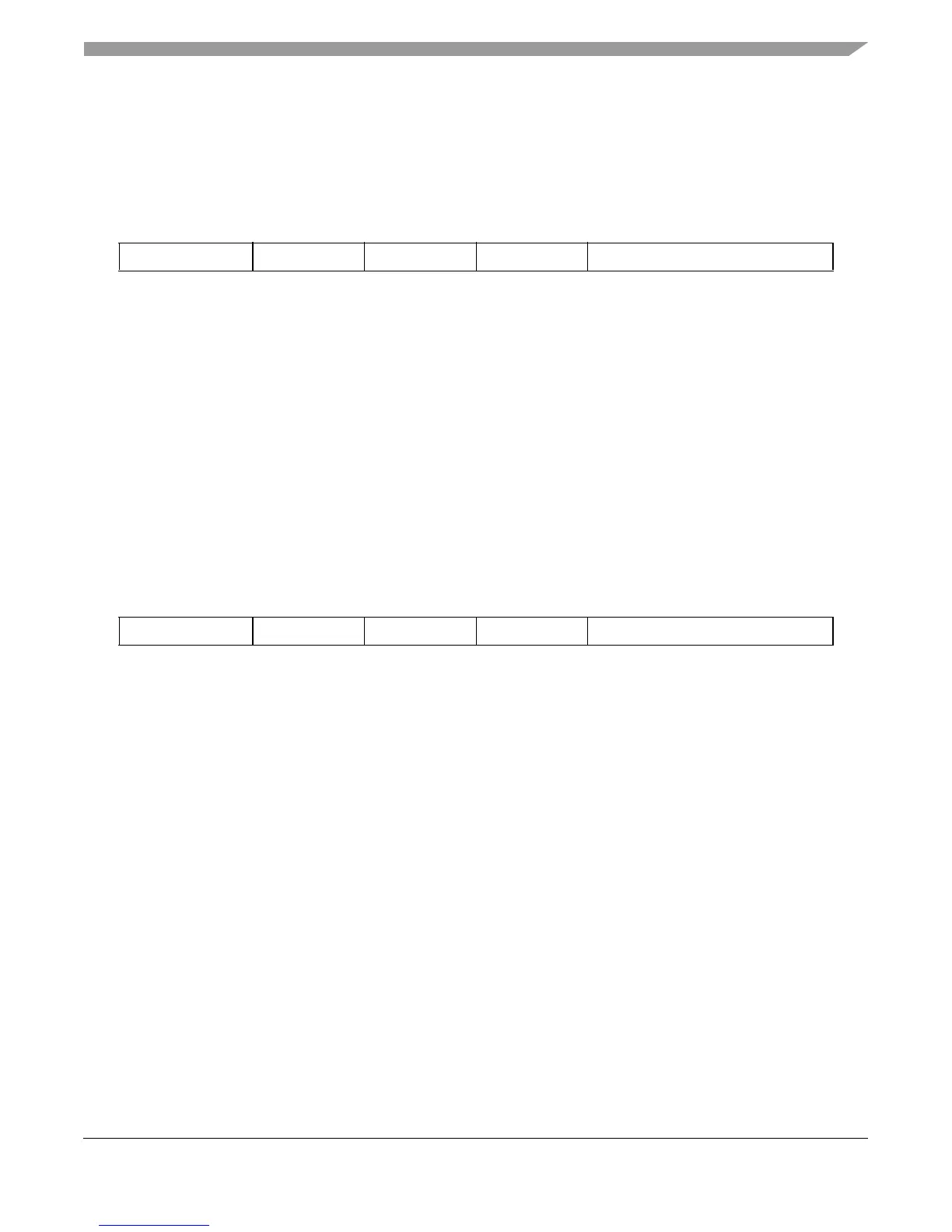

0 56 101115162021 31

000100 rD rA 0 00000 1011100101

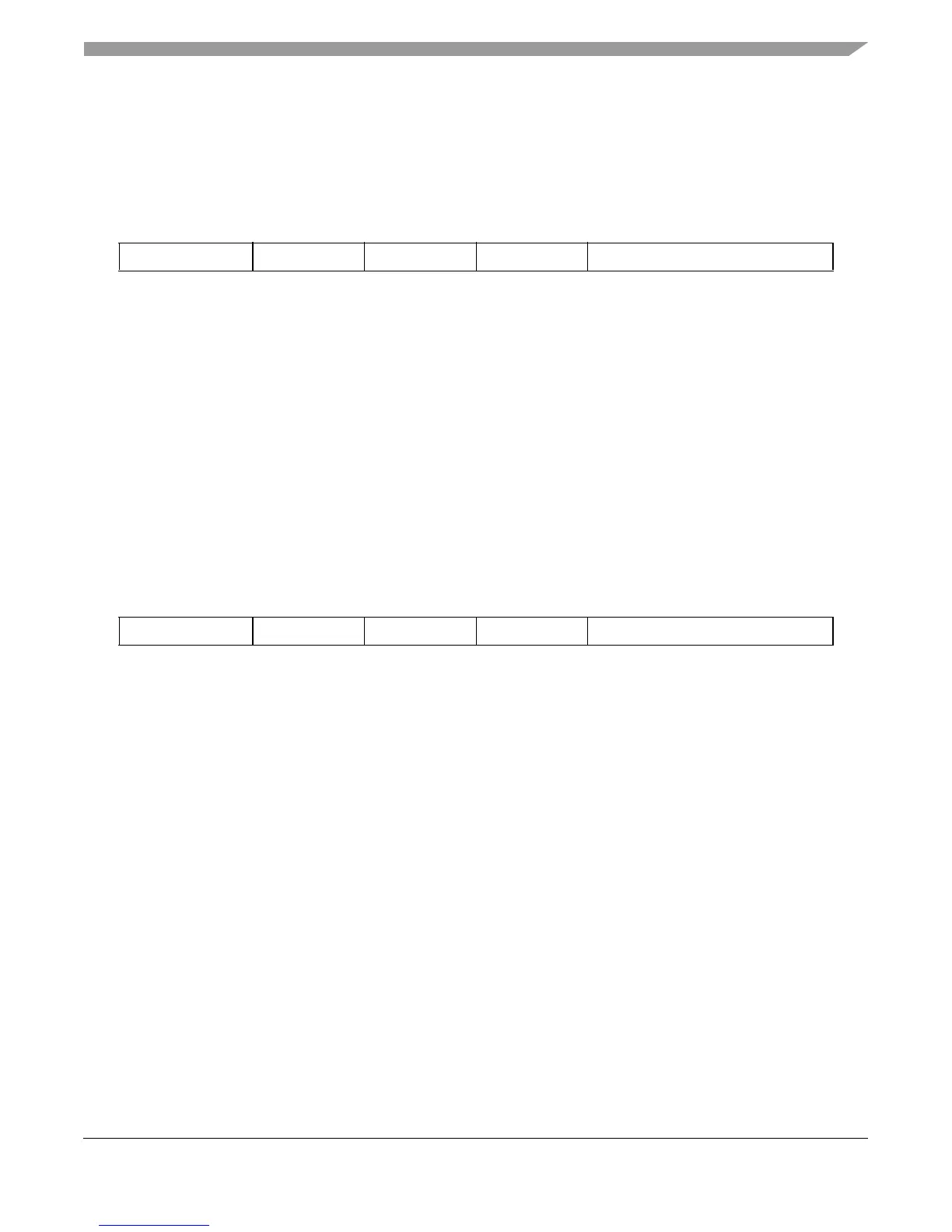

0 56 101115162021 31

000100 rD rA 0 00000 1011100110

Loading...

Loading...